# APPLE® INTERFACING JONATHAN A. TITUS DAVID G. LARSEN CHRISTOPHER A. TITUS

## The Blacksburg Continuing Education<sup>™</sup> Series

The Blacksburg Continuing Education Series<sup>™</sup> of books provide a Laboratory—or experimentoriented approach to electronic topics. Present and forthcoming titles in this series include:

- Advanced 6502 Interfacing

- Analog Instrumentation Fundamentals

- Apple Interfacing

- Basic Business Software

- BASIC Programmer's Notebook

- Circuit Design Programs for the Apple II

- Circuit Design Programs for the TRS-80

- Design of Active Filters, With Experiments

- Design of Op-Amp Circuits, With Experiments

- Design of Phase-Locked Loop Circuits, With Experiments

- Design of Transistor Circuits, With Experiments

- Design of VMOS Circuits, With Experiments

- 8080/8085 Software Design (2 Volumes)

- 8085A Cookbook

- Electronic Music Circuits

- 555 Timer Applications Sourcebook, With Experiments

- Guide to CMOS Basics, Circuits, & Experiments

- How to Program and Interface the 6800

- Introduction to FORTH

- Microcomputer—Analog Converter Software and Hardware Interfacing

- Microcomputer Interfacing With the 8255 PPI Chip

- Microcomputer Design and Maintenance

- NCR Basic Electronics Course, With Experiments

- NCR Data Communications Concepts

- NCR Data Processing Concepts Course

- NCR EDP Concepts Course

- PET Interfacing

- Programming and Interfacing the 6502, With Experiments

- 16-Bit Microprocessors

- 6502 Software Design

- 6801, 68701, and 6803 Microcomputer Programming and Interfacing

- The 68000: Principles and Programming

- 6809 Microcomputer Programming & Interfacing, With Experiments

- TEA: An 8080/8085 Co-Resident Editor/Assembler

- TRS-80 Assembly Language Made Simple

- TRS-80 Interfacing (2 Volumes)

- TRS-80 More Than BASIC

In most cases, these books provide both text material and experiments, which permit one to demonstrate and explore the concepts that are covered in the book. These books remain among the very few that provide step-by-step instructions concerning how to learn basic electronic concepts, wire actual circuits, test microcomputer interfaces, and program computers based on popular microprocessor chips. We have found that the books are very useful to the electronic novice who desires to join the "electronics revolution," with minimum time and effort.

> Jonathan A. Titus, Christopher A. Titus, and David G. Larsen "The Blacksburg Group"

Bug symbol trademark Nanotran, Inc., Blacksburg, VA 24060

# APPLE<sup>®</sup> INTERFACING

by .

Jonathan A. Titus, David G. Larsen, and Christopher A. Titus

Howard W. Sams & Co., Inc. 4300 WEST 62ND ST. INDIANAPOLIS, INDIANA 46268 USA Copyright © 1981 by Jonathan A. Titus, Christopher A. Titus, and David G. Larsen

#### FIRST EDITION SECOND PRINTING-1982

All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-21862-3 Library of Congress Catalog Card Number: 81-84282

Edited by: Bob Manville Illustrated by: Jill E. Martin

Printed in the United States of America.

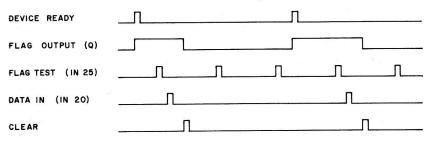

# Preface

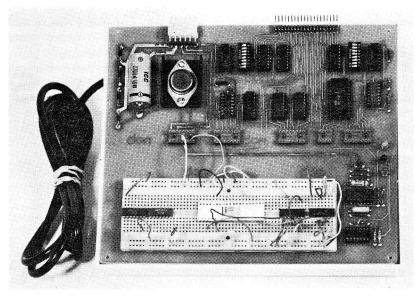

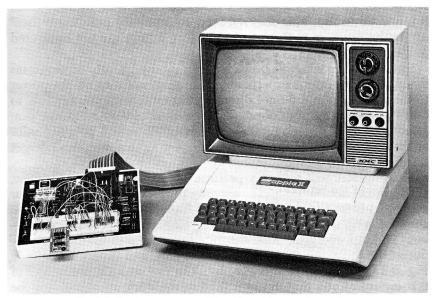

The purpose in writing this book is to introduce you to the signals within the Apple<sup>®\*</sup> II computer and to show you how these signals can be used to control external devices under the control of BASIClanguage programs. A general-purpose computer interface breadboard has been developed to speed your circuit design and testing so that you can easily perform the many interesting experiments that are included in the book. By using a design system such as the one described in this book, you will spend your time concentrating on the principles involved, rather than troubleshooting your circuits. However, you will have the opportunity to build and test many digital circuits, as well as circuits that use digital-to-analog and analogto-digital converters.

.

We have chosen to use the Apple II computer with 16K of read/ write memory, and the Applesoft<sup>TM</sup><sup>†</sup> BASIC interpreter program. This software provides a great deal of flexibility and it is worth having it available when you are using external interface circuits. The Applesoft BASIC interpreter has two general-purpose commands that can be used to transfer information to and from the computer. These instructions are easily mastered, without requiring a detailed understanding of the 6502 microprocessor integrated circuit (IC) that is used as the "heart" of the Apple.

First we will introduce you to the control signals that are available from the Apple computer for interfacing, and we will show you how they are used. Some of the signals will not be described, since they are generally not used in interface circuits, and are meant to be used by special interface devices that are manufactured commercially.

Our next step is to show you how the Apple can identify or address external devices through the use of two general-purpose instructions, PEEK and POKE. These commands are central to the control of external devices; we spend some time covering their operation and the use of a variety of circuits that can be used to identify specific input/ output, or I/O devices. You will also see how the Apple can transfer information to and from external devices over the bidirectional data

\*Apple and Apple II are registered trademarks of Apple Computer, Inc.

Applesoft is a trademark of Apple Computer, Inc.

bus; the basic circuits used for *input ports* and *output ports* are described in detail. Real circuits are provided, so that you can quickly use the many examples in designing your own interface devices.

You will also see the power of BASIC-language programs—as the data is processed within the computer to provide meaningful results. Simple control programs are provided to show you how BASIC-language programs and I/O devices can interact. You will be able to write simple control and data processing programs to go along with your I/O ports and devices.

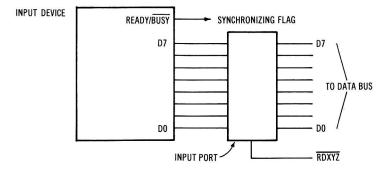

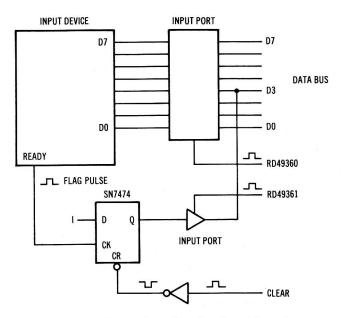

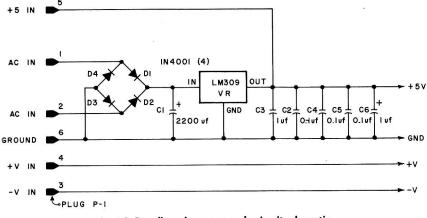

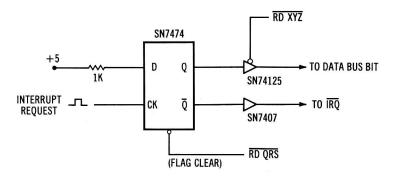

Since the computer is not always synchronized to external devices, there must be some interaction between the computer and the various I/O devices so that each knows when the other is ready for some appropriate action. This leads us to the topic of flags—those signals that are used by the computer and by external I/O devices to allow information to be transferred in an orderly fashion. Since flags are important, we spend some time on them and on the corresponding circuits that are actually used in external devices. Software is covered too, since the flag circuits are useless unless they can be sensed by a control program.

We have assumed that you have a fairly good understanding of the commands in Applesoft BASIC. If you are just getting started with the Apple computer, we hope that you will take some time to review the simple commands, such as FOR, GOTO, IF . . . THEN, PRINT, and INPUT. Other commands will be introduced in the text and experiments, and we will provide the details of their operation. At the end of this book, the use of these and other commands should be second-nature.

In Chapter 6, we have provided 16 detailed, step-by-step experiments that you can perform to reinforce the many interfacing principles that have been developed in the text. You will also see the power of BASIC-language programs for interface control and for actually processing the information that is involved in transfers to and from I/O devices. We have made an effort to cover a broad spectrum of interesting interface applications. Throughout the experiments, you will see that the same basic principles apply to all of the interface circuits, from the simplest to the most complex.

We realize that it is difficult to write a book like this for an audience that has a wide range of backgrounds, from the beginner to the advanced user. Thus, we have chosen to start at some middle point. We have chosen to skip basic binary numbering, decimal-to-binary conversions, basic digital electronics, and breadboarding. These topics are covered in detail in other books, and the reader who is in the middle of our assumed spectrum of readers probably has a good understanding of these topics. In some places, a paragraph or two of review material have been provided, just to serve as a refresher. We make no attempt to provide much detail here, simply enough to get you started.

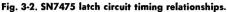

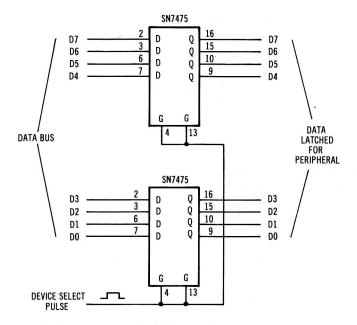

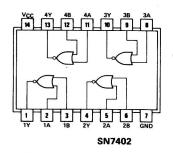

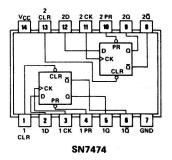

We have assumed some familiarity with SN7400-family digital integrated circuits, or chips, such as the SN7402 quad NOR gate and the SN7475 quad latch chip. Other complex chips will be introduced and explained in sufficient detail so that you can use them as shown in the text or experiments. If you wish to use these devices in other applications, we suggest that you obtain the necessary data sheets from the manufacturers. The data sheets will provide the necessary information for a wide variety of uses, and they will also reflect any basic changes or modifications that may have been made to an "updated" device, or one that has been "enhanced" with some special feature.

The Apple II computer has eight general-purpose 50-conductor interface connectors in its case. The basic bus signals used in the experiments are derived from the signals at these connectors, so if you decide to design and build some of your own interface circuits that will be plugged into one of these "slots," you will find the same signals are readily available at the edge connectors. However, there are also some special-purpose signals that are generated by the Apple to make the interfacing task somewhat easier. These signals and their uses are described in detail in Chapter 7. Since the signals are not general purpose, but are specific to the Apple, and in many cases, specific to a particular connector, they are described last. To show you how these signals are used, a simple asynchronous-serial communication interface circuit is described, and software to control it is listed. This type of interface can be used to communicate with other computers, serial printers, modems, and other interface devices that use the asynchronous-serial data format.

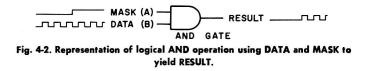

We have not described assembly-language programming, since this is a specialized topic and requires a great deal of background. However, we have provided one simple assembly-language subroutine for you to use in several of the experiments. There is a good reason for including this subroutine; the equivalent function is not readily available in Applesoft. The function required is the logical ANDing of 8-bit bytes. The logical AND in Applesoft is simply a trueor-false AND operation, and it cannot be easily used for bit ANDing. The assembly-language subroutine also provides you with an introduction to how such routines can be accessed by a BASIC-language program. We have chosen to use the more complicated USR(X) command, rather than the CALL command, since we think that more will be learned.

We found that there were some limitations to the Apple. For example, there is no simple "rounding" command that can be used to round a number to a specific number of decimal digits, for example 4.1986 to 4.20. Likewise, the absence of a bit-by-bit ANDING command was a limitation that was overcome with an assembly-language routine. We also found that the potentially useful WAIT command that is used to test individual bits will "hang up" the computer if the condition is not found. The computer continues to wait if the condition is not met, and you must reset the computer to get your program going again. A color display and nice graphics are available, although we used a black/white monitor in our system.

Most of the special purpose chips, such as the analog converters, have been chosen because of their simplicity, low cost, and availability. This is not meant to be an endorsement of these products. As your interfacing sophistication increases, you will find other specialpurpose devices that can serve the same function, but perhaps with added features, more resolution, different power supplies, etc. Our aim is to get you started, and not to provide you with a sourcebook of every possible interface to the Apple computer system. An impossible task in any case.

If you are interested in some additional reading about more advanced topics, we recommend:

6502 Software Design (21656).

Programming & Interfacing the 6502, With Experiments (21651). Microcomputer-Analog Converter Software and Hardware Interfacing (21540).

We also recommend TRS-80 Interfacing, Book 2. While written around the TRS-80 computer, this book details more advanced interfacing topics such as driving high-current/high-voltage loads, serial communications, remote control, analog converters, filtering and data processing, and other interesting topics. You will quickly see that the similarities between the TRS-80 and Apple are much greater than their differences. Control signals and BASIC commands are almost identical. All of the books noted above are available from Howard W. Sams & Co., Inc., 4300 West 62nd Street, Indianapolis, IN 46268.

The pin configuration figures used in most of the figures, unless otherwise noted, are provided through the courtesy of Texas Instruments, Incorporated. The names Apple and Applesoft are trademarks of Apple Computer, Inc., Cupertino, CA. The name TRS-80 is a registered trademark of Radio Shack.

We hope that you enjoy this book, and that it leads you to design and build some interface circuits of your own.

JONATHAN A. TITUS, CHRISTOPHER A. TITUS and DAVID G. LARSEN "The Blacksburg Group"

# Contents

#### **CHAPTER 1**

| 6502 | Processor    | •    | •     | •   | •    | • | • 27    | •     | •    | •   | •   | ٠     | ٠    | ٠  | 9 |

|------|--------------|------|-------|-----|------|---|---------|-------|------|-----|-----|-------|------|----|---|

|      | Memory-Input | :/01 | ıtput | t ( | I/O) | D | evices– | -Soft | ware | I/( | 0 C | Contr | ol I | n- |   |

|      | structions   |      |       |     |      |   |         |       |      |     |     |       |      |    |   |

#### **CHAPTER 2**

| Apple | INTERFACING | • | • |  | • | • | • | • | • | • | • | • | 26 |

|-------|-------------|---|---|--|---|---|---|---|---|---|---|---|----|

|       |             |   |   |  |   |   |   |   |   |   |   |   |    |

I/O Device Address Decoding–Device Addressing

#### **CHAPTER 3**

#### **CHAPTER 4**

I/O Device Synchronization-Logical Operations and Flags-Flag-Detecting Software-Assembly-Language Logical Operations-Complex Flags-Flag Circuits-Multiple Flags-Interrupts-Final Words

#### **CHAPTER 5**

00

| BREADBOARDING WITH T | HE APPLE     |     | •  |      | •    | •    | •    | •    | •    | •  | 05 |

|----------------------|--------------|-----|----|------|------|------|------|------|------|----|----|

| Basia Breadboard_Co  | nnections to | the | An | nle- | -Oth | er ( | Cons | ider | atio | ns |    |

#### **CHAPTER 6**

| Apple Interface Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

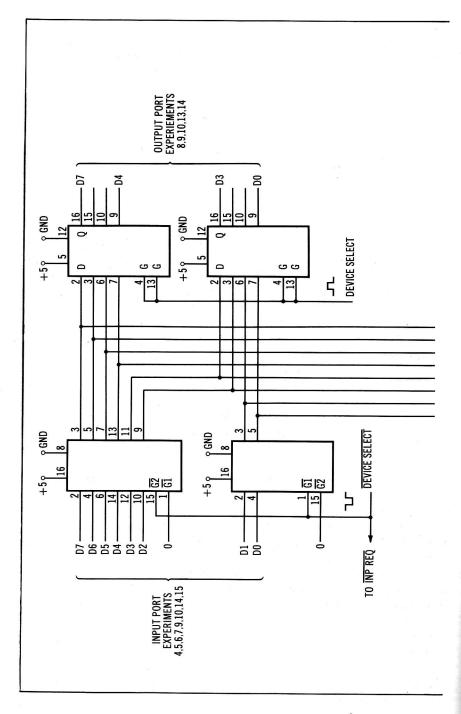

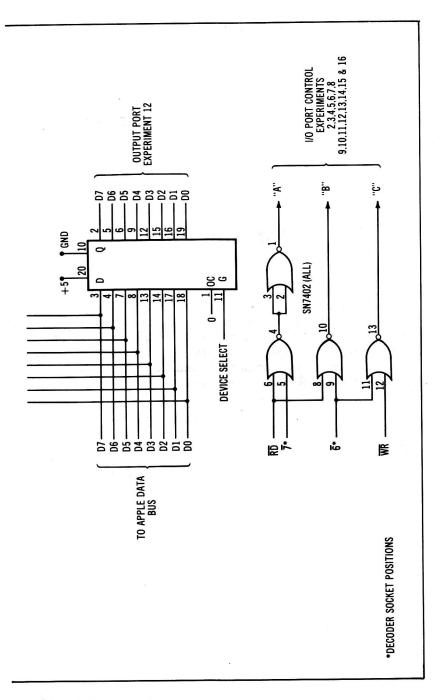

| Introduction to the Experiments-Use of the Logic Probe-Use of the<br>Device Address Decoder-Using Device Select Pulses-Constructing<br>an Input Port-Multibyte Input Ports-Input Port Applications-In-<br>put Port Applications (II)-Constructing an Output Port-Output<br>Port and Input Port Interactions-Data Logging and Display-Simple<br>Digital-to-Analog Converter-Output Ports, BCD and Binary Codes<br>-Output Ports Traffic Light Controller-Logic-Device Tester-Sim-<br>ple Flag Circuits-A Simple Analog-to-Digital Converter |

| CHAPTER 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| On the Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interface Control Signals-An Interfacing Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| APPENDIX A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Logic Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| APPENDIX B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Parts Required for the Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### APPENDIX C

| 6502 Microprocessor Technical Data |  | ۰. |  |  | • |  | 185 |

|------------------------------------|--|----|--|--|---|--|-----|

|------------------------------------|--|----|--|--|---|--|-----|

### APPENDIX D

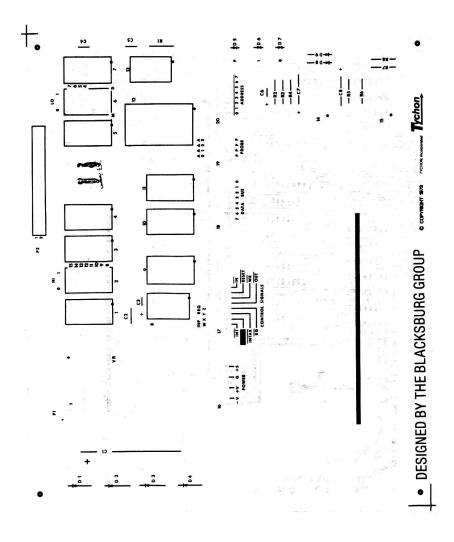

| Apple Interface Breadboard Parts | Apple | INTERFACE | Breadboard | Parts | • | • |  |  | • | • | • | • | 195 |

|----------------------------------|-------|-----------|------------|-------|---|---|--|--|---|---|---|---|-----|

|----------------------------------|-------|-----------|------------|-------|---|---|--|--|---|---|---|---|-----|

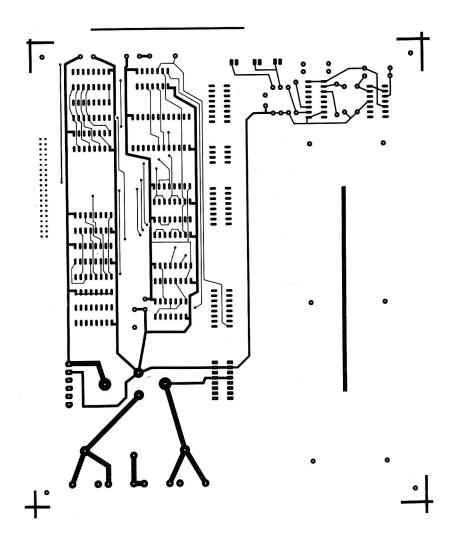

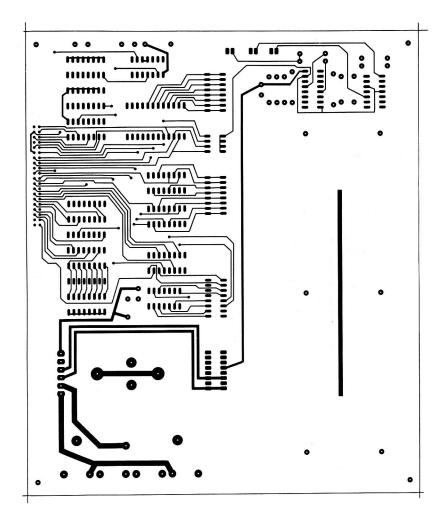

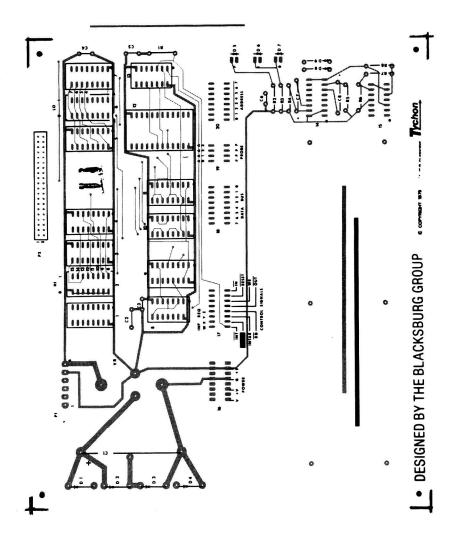

## APPENDIX E

| PRINTED | -Cr | RCUIT | r E | BOARD | Ar | rwo | RK | • | • | • | • | • | • | • | 197 |

|---------|-----|-------|-----|-------|----|-----|----|---|---|---|---|---|---|---|-----|

|         |     |       |     |       |    |     |    |   |   |   |   |   |   |   |     |

| INDEX   |     |       | 2   |       |    |     |    | • | • |   |   |   |   |   | 203 |

# CHAPTER

# 6502 Processor

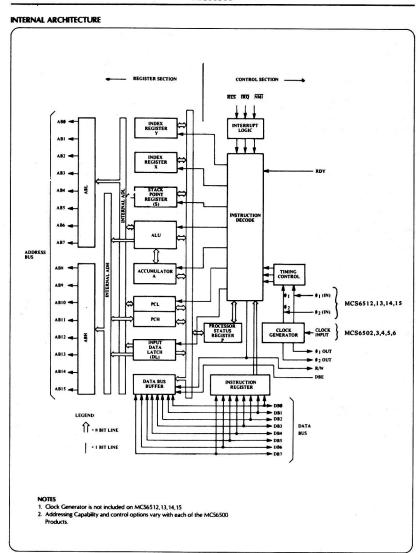

The Apple II® (Apple®) computer system by Apple Computer, Inc., uses the 6502-type of microprocessor integrated circuit. This "chip" forms the heart of the central processing unit (CPU) of the computer, the place where the actual mathematical, logical, decisionmaking, and other operations take place. The 6502-type microprocessor chip is manufactured by MOS Technology (Norristown, PA 19401), Rockwell International (Anaheim, CA 92803) and Synertek Corporation (Santa Clara, CA 95051).

The 6502 is an 8-bit processor. Thus, all of the mathematical, logical, data transfer, input and output operations operate on eight binary bits at a time. Each bit, of course, can be either a logic one or a logic zero. The 6502 uses an 8-bit data bus to transfer information between itself and various memory locations and input/output (I/O) devices such as a keyboard, printer, etc. In cases where the value of the information exceeds the limit of eight bits, multiples of 8-bit data words are used. Each 8-bit data word is generally referred to as a *byte*.

You should realize that the maximum value that can be expressed with eight bits is  $1111111_2$  or  $255_{10}$ . If larger values are to be operated on in an 8-bit computer system, then multibyte operations are required. Generally, this means that corresponding data bytes in two data words are operated on, followed by the operation being performed on the next corresponding set of bytes in the large data words. In this way large values, beyond the value of 255, may be readily processed. It is important to remember, though, that the

Apple and Apple II are registered trademarks of Apple Computer, Inc.

Apple CPU can only process and transfer eight bits or one byte at a time.

The 6502 uses a single set of eight pins to make the connection with the data bus in the computer. This data bus is used to transfer information both to and from the computer. This type of a bus is called *bidirectional*, since it allows information to flow in two different directions. This is much like a highway that is used to allow vehicles to drive one way in the morning and to allow vehicles to travel in the opposite direction in the evening.

The 6502 generates control signals on the integrated circuit that are used both internally and externally to supervise and manage the flow of information on the bus, in one direction at a time. We will explore the generation and use of these signals later in this book.

#### MEMORY

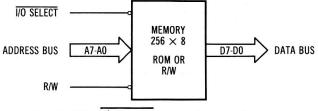

All computer systems have some memory associated with them. In general, the memory is used to store both a program that will control the operation of the computer, as well as the information that is to be processed. In the 6502 computer, each memory location can be used to store eight bits of information, or one byte of data. Most memories consist of multiples of these one-byte storage locations, generally in multiples of 1024, abbreviated 1K.

The memory locations must be addressed in some way so that the computer knows exactly where it is to store data or obtain program step information. The 6502 microprocessor chip has 16 address outputs allowing it to specify any one of  $2^{16}$  or 65,536 memory locations, each of which can contain one byte. This is often shortened to 64K, indicating that 64K *bytes* of information can be addressed. In almost all microcomputer memory systems, each memory location is uniquely addressed with a 16-bit address.

The address bus lines are labeled A0 through A15, corresponding to the least-significant bit (LSB) through the most-significant bit (MSB), respectively. The LSB and MSB can both be either a logic one or a logic zero, but their *position* gives the LSB a *value* of zero or one and the MSB a *value* of zero or 32,768. Since the 6502 is an 8-bit processor, the address lines are frequently split into two groups of eight lines each, A7-A0 and A15-A8. The lines A7-A0 are referred to as the low or LO address, while lines A15-A8 are referred to as the high or HI address. In many 6502-based computers, the HI address is also called the *page address*, since the memory may be arbitrarily divided into 256 pages, with 256 bytes per page. The uses of the address bus will be explored further when software instructions are discussed and when interface circuits are developed. Unlike the data bus, the address bus is unidirectional, the address information flows

| VSS<br>RDY<br>#1(OUT)<br>IRQ<br>N.C.<br>NMI<br>SYNC<br>VCC<br>A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | 40<br>39<br>38<br>37<br>36<br>35<br>34<br>33<br>32<br>29<br>28<br>27<br>26<br>25<br>24<br>25<br>24<br>23<br>22<br>22<br>21 | $\begin{array}{l} \hline \text{RES} \\ \Phi_2(\text{OUT}) \\ \text{S.O.} \\ \Phi_0(\text{IN}) \\ \text{N.C.} \\ \text{N.C.} \\ \text{R/W} \\ \text{D0} \\ \text{D1} \\ \text{D2} \\ \text{D3} \\ \text{D4} \\ \text{D5} \\ \text{D6} \\ \text{D7} \\ \text{A15} \\ \text{A14} \\ \text{A13} \\ \text{A12} \\ \text{VSS} \end{array}$ |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                      |                                                                                                             |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                      |

#### Fig. 1-1. 6502 Microprocessor chip pin configuration.

in only one direction, from the CPU to the memory and to external devices.

The pin configuration of the 6502 is shown in Fig. 1-1. Although most of the other signals may be meaningless to you now, you should be able to identify the 8 data bus input/output pins and the 16 address output pins.

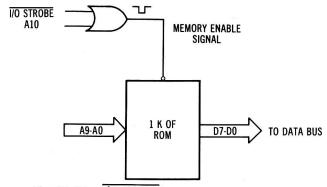

Since the memory section is being discussed, there are two basic types of memory devices used in microcomputer systems. They are:

- 1. Read/Write-Read/Write (R/W) memory is used for the storage of data that will be changed or updated. The computer must be able to place the information in a memory location and then be able to read it back. Programs that will change are also stored in R/W memory for the same reason. The lowest cost Apple computer contains 16,384 or 16K bytes of R/W memory.

- 2. Read-Only—Read-only memory (ROM) is used when data values and program steps will not be altered. The BASIC interpreter program in your Apple system is contained in read-only memory chips. The Apple BASIC interpreter is stored in 12K of ROM.

There are various sub-classes of these types of memory devices. The R/W memories may be either *static* or *dynamic*. Static memory chips will maintain the values stored in them until they are changed. Dynamic memories require refreshing by external hardware every few milliseconds or they will "forget" or lose the data stored in them. The R/W memories in the Apple are dynamic, with the necessary refreshing circuitry contained on the computer printed-circuit board.

There are many types of read-only memories. The various types are generally all static, the differences occurring in the means of storing the 8-bit values in the memory locations. The two most important types are *mask-programmed* and *field-programmed*. The mask-programmed devices have data values, program steps, etc., stored in them during the various manufacturing steps. They are generally referred to as ROMs. The field-programmable devices require some kind of special programming circuitry to store the logic ones and zeros in the various locations. Some of the field programmable ROMs, or PROMs, as they are generally called, can be erased under high-intensity ultraviolet light. They can then be reprogrammed. This is very useful when programs are being developed that will be stored in read-only memory. It does not require the development of masks and chips—an expensive process—each time a program bug is found or a change is made.

A few final words are required about semiconductor memory devices. The read-write devices are *volatile*, since data (your program and values) will "evaporate" or disappear when power is removed from the system. The read-only memories, on the other hand, are considered to be nonvolatile, since they will maintain the data or program steps (the BASIC interpreter) when the power has been removed.

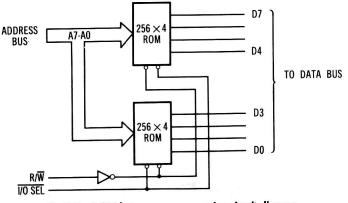

Most memory integrated-circuit packages or chips do not have all 16 of the address lines connected to them. They have only enough address connections to uniquely address the memory locations within the individual chip. Thus, a 64-byte chip, small by standards of today, would only have 6 address line inputs while a 1024 (1K) byte memory chip would have 10 address line inputs. Memory chips such as these have an additional control or chip-enable input that allows banks or groups of the chips to be selected, one set at a time. Various decoding and selecting circuits may be used, thus allowing a 32K block of memory to be constructed from 64-byte or 1K byte chips, or even combinations of the two. The main point here is that the memory chips do not require all 16 address lines to be connected directly to them, although some combination of all 16 address bits will be used to uniquely select one byte. You should not be confused when you are confronted with a  $1K \times 4$  bit memory that only has 10 address inputs and a chip enable input. This concept will be developed further as you study input/output data transfers.

One control signal is generated by the 6502 processor chip to control the flow of information on the data bus. This signal is noted as READ/WRITE, or more simply, R/W. Whenever a read, or a write, operation is to take place, the 6502 must specify a 16-bit address to locate the memory "cell" that is to be involved in the transfer. In this case, the cell is an 8-bit word or byte.

The "bar" over part of the signal notation indicates that when the signal is a logic zero, a write operation is taking place; and when in the logic one state, a read operation is taking place. Thus, a single line controls all of the memory functions. In some 6502-based computer systems and peripherals, you may see the signal "split," to provide two memory control signals, memory read (MEMR or  $\overline{MR}$ ), and memory write (MEMW or MW). This takes some additional gating, so in most cases, the  $R/\overline{W}$  signal is used by itself. It is available at pin 34 on the 6502 microprocessor chip.

You may also see the notation RAM used to incorrectly signify read/write memory. The acronym RAM stands for *random-access memory*. In fact, all of the modern, easy-to-use memory devices are random access, since one may address one location and then any other, without having to sequence through all of the locations between the two addresses.

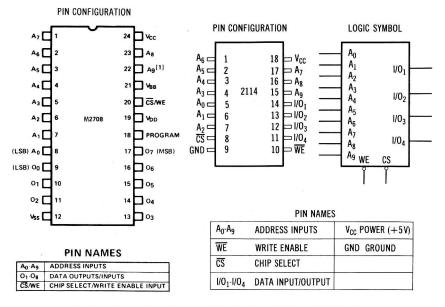

Pin configurations for typical memory chips have been provided in Fig. 1-2.

For additional information about memory devices, we refer you to

• Intel Memory Design Handbook, Intel Corporation, Santa Clara, CA 95051, 1975.

Fig. 1-2. Pin configuration for 2708 1K  $\times$  8 PROM and 2114 1K  $\times$  4 R/W memory.

- The 8080A/9080A MOS Microprocessor Handbook, Advanced Micro Devices, Inc., Sunnyvale, CA 94086, 1977.

- Mostek Memory Products Catalog, Mostek Corporation, Carrollton, TX 75006, 1977.

- Bipolar and CMOS Memory Data Book, Harris Semiconductor Prod. Div., Melbourne, FL 32901, 1978.

#### INPUT/OUTPUT (I/O) DEVICES

Most microcomputer-based systems are worthless without some attached I/O devices. These devices may be standard peripherals, such as card readers, printers, displays, or they may be sensors, controllers, and other devices that most people do not normally associate with computers. The Apple is no exception. It already has several I/O devices associated with it: a television display, a cassette recorder, and a keyboard.

Other I/O devices can be added to your computer. These devices may be of your own design or they may be standard, commercially available devices that are compatible with the Apple. These I/O devices are much like the individual memory locations that were discussed in the previous section. The I/O devices are attached to the data bus, since data is transferred to them and from them, and they are also connected to the address bus so that they may be uniquely addressed by the 6502 microprocessor chip.

A control signal, READ/ $\overline{WRITE}$  or R/ $\overline{W}$ , is used to synchronize the flow of data to and from the I/O devices. This signal is also used in 6502-based computer systems to control the flow of information to and from the memory chips. Thus, there is no differentiation between memory addresses and I/O device addresses in 6502-based computers. In computers that are based upon the 8085- or Z-80-type microprocessor chips, there are different techniques that are used to address memory and I/O devices independently. Since only one synchronizing signal is used to control memory and I/O devices, the Apple's 6502 processor will be either reading or writing at all times. When the R/ $\overline{W}$  signal is a logic one, the 6502 is reading information from the data bus. When the  $R/\overline{W}$  signal is a logic zero, the 6502 is writing data to an external I/O device, or to a memory location. The "bar" over the W simply means that the write operation takes place when the  $R/\overline{W}$  signal is a logic zero. You may see other signals with such bars over their names. This simply means that the signals are active in the logic zero state.

Since we will be concentrating on the use of I/O devices with the Apple, we have left a great deal of the specific discussion to the remaining sections.

#### Review

At this point, you should understand that the 6502 transfers and operates on eight bits of data at a time. Complex calculations and operations often require multiple groups of eight bits or bytes. The bytes are transferred to and from the 6502 CPU on an 8-bit bus.

| DATA BUS       | D7-D0  | An 8-bit bidirectional set of lines for transfer of information between the CPU and I/O devices. |

|----------------|--------|--------------------------------------------------------------------------------------------------|

| ADDRESS BUS    | A15-A0 | A 16-bit unidirectional address bus used to ad-<br>dress both memory and I/O devices.            |

|                | A15-A8 | HI address bus, most-significant eight address<br>bits.                                          |

|                | A7-A0  | LO address bus, least-significant eight address bits.                                            |

| CONTROL SIGNAL | R/₩    | Read/write control signal.                                                                       |

| Table 1-1. Control Signals Used for Interfacing | Table | e 1-1. Control | Signals | <b>Used</b> for | Interfacing |

|-------------------------------------------------|-------|----------------|---------|-----------------|-------------|

|-------------------------------------------------|-------|----------------|---------|-----------------|-------------|

NOTES: The "bar" notation, i.e.,  $\overline{W}$ , indicates a logic zero is the "active" state, the state that causes the corresponding action to take place.

In each case in which a signal is enumerated, the numbers increase as the significance of the bits increases, i.e., A15 = most-significant address bit (MSB).

The 6502 uses a 16-bit address bus to address individual memory location and I/O devices. The address bus is frequently broken into a HI and LO address bus, of eight bits each. The single control signal, R/W, controls the flow of information to and from the 6502 CPU. The signals and their designations are noted in Table 1-1.

#### SOFTWARE I/O CONTROL INSTRUCTIONS

#### I/O Commands

The Apple computer has a number of instructions that are used to control I/O devices. For the most part, though, these instructions are used to control specific I/O devices or to perform specific functions. Without realizing it, you are already familiar with some, if not all, of these I/O instructions.

Here are some specific examples of these I/O control instructions, to refresh your memory.

The INPUT and PRINT commands are probably familiar to you. The INPUT command causes a BASIC program to stop and wait for an input from the keyboard. The PRINT command causes an answer or string of characters to be "printed" on the tv screen.

#### Example 1-1. A Simple I/O Program

10 INPUT "VALUE OF X IS"; X

20 PRINT " INPUT VALUE WAS"; X

If you executed the program in Example 1-1, the value associated with the variable, X, would have to be entered into the computer before the program passed control to statement 20. These two types of I/O statements are frequently used to allow an operator to enter a value and to see it displayed. There are many variations of both the INPUT and PRINT commands, but these two examples serve to illustrate the point; you have already been using I/O operations in BASIC-language programs without difficulty.

You may have already discovered that there are also graphic display I/O commands in BASIC, too. These are commands such as HOME, PLOT X,Y and SCRN (X,Y). The HOME command clears the screen, and places the blinking cursor at the "home" position in the upper left-hand corner of the tv screen. The PLOT and SCRN commands require the use of "coordinates" to indicate where an operation is to take place.

The program in Example 1-2 shows how some simple graphic display commands are used in a short program. This program generates a display of randomly changing colored dots on the tv screen. If you are using a black-and-white (b/w) tv, you will see the dots in varying shades of gray.

#### Example 1-2. A Random Color Pattern Generator Using I/O Commands

10 GR 20 X=INT(40\*RND(1)) + 1 30 Y=INT(40\*RND(1)) + 1 40 COLOR=INT(15\*RND(1)) + 1 50 PLOT X,Y 60 GOTO 20

There are two other commands that you may not have considered to be I/O commands. These are the LOAD and SAVE commands that are used to read and store programs on cassette tapes. Each command causes a preset series of operations to take place, controlling the cassette recorder. The use of these commands is fairly obvious, so we will not provide an example.

Other I/O commands are the IN#X and PR#X operations that are associated with special I/O devices that can be substituted for the keyboard and tv display. It is important that you realize that these I/O instructions are specific to the Apple computer and its BASIClanguage interpreter program. These instructions would be meaningless to other 6502-based computer systems, unless they used the Apple BASIC program. The instructions are also specific to one I/O device, i.e., the HOME command will not have an effect on the cassette recorder, or any other I/O device. Likewise, the INPUT command controls the input of values only from the keyboard on the console.

#### General-Purpose I/O Commands

Although there are some general-purpose I/O commands in the INTEGER BASIC interpreter program for the Apple computer, for this book we have chosen to use what we consider to be the more flexible APPLESOFT BASIC interpreter program. If you wish to convert your Apple computer to this program, a local Apple computer dealer can assist you.

The two I/O device commands are PEEK and POKE. They are used to transfer data to an external device from the computer (POKE), and to the computer from an external device (PEEK). There is a specific format for these instructions that must be used if the instructions are to operate properly.

Input and output devices will be referred to as *ports*. Thus, an output device will be an *output port* and an input device will be an *input port*. This is standard nomenclature used throughout the micro-computer industry.

The output instruction, POKE, must specify the *address* of the I/O device that is to be involved in the transfer of data and also the value that is to be transferred to the addressed device. The actual format for the POKE instruction is POKE, x,y, where the x value represents the *decimal* address of the output device that is to receive the data value, y. The data, y, must also be a decimal number. Since the 6502 microprocessor chip can address 65536 memory locations, the address must be within the range of 0 to 65535, inclusive. The data value must be within the range of 0 to 255, inclusive, since the computer uses an 8-bit data bus for all data transfers, and the largest number that can be transferred on such a bus is 255.

The value 215 is sent to output port 12684 in the following statement: POKE 12684,215.

The input instruction, PEEK, is similar to the POKE instruction, except that no data value is incorporated into the command. We are interested in determining the value present at the specific input device, so only the decimal address of the input device is specified; PEEK (x), where x is the decimal address of the input device.

It does little good to input a value without doing something with it, so the input command is always incorporated in a complete statement, rather than being a statement by itself. An example of this is Q=PEEK(34579).

In this case, the variable, Q, is assigned the decimal value that has been input from device 34579. It is important that you remember to enclose the address of the input device in parentheses.

Whenever a PEEK command is used, the value that is input will be between 0 and 255, inclusive. Again, this is due to the limitation of 8-bit transfers.

Table 1-2. Valid Input (PEEK) and Output (POKE) Command Structures

| POKE 45124,98<br>POKE N,120<br>POKE 45124,X<br>POKE X,M | L = PEEK (23109) $L = PEEK (Q)$ |

|---------------------------------------------------------|---------------------------------|

| POKE X,M                                                |                                 |

The input and output commands may have variables specified within them, rather than specific values for port addresses, and in the case of the POKE command, data values. Thus, all of the PEEK and POKE commands shown in Table 1-2 are valid. We have assumed, of course, that the values for the variables, N, M, X and Q have been specified somewhere in the program prior to the use of the instructions shown in Table 1-2.

Input and output commands in which the address values exceed 65535 will generate an ILLEGAL QUANTITY ERROR in the Apple computer. An attempt to output a numerical data value that exceeds 255 will also generate an ILLEGAL QUANTITY ERROR.

We have provided some examples that show the use of the POKE and PEEK commands. While the programs shown in Example 1-3 can be executed, they will not do anything useful, since you do not have any external I/O ports connected to your computer, at present.

### Example 1-3. Simple I/O Programs for PEEK and POKE Commands

```

10 INPUT "OUTPUT PORT # =";P

20 INPUT "VALUE FOR OUTPUT"; V

30 POKE P,V

40 GOTO 10

```

```

10 INPUT "INPUT PORT \# = "; M

20 PRINT "VALUE AT PORT ="; PEEK (M)

30 GOTO 10

```

Since 6502-based computers cannot distinguish between memory locations that are used for the temporary storage of programs and data, and those that are being used for I/O ports, the PEEK and POKE instructions are frequently used to examine and alter the contents of various memory locations within the Apple. If you POKE information into read/write memory in an indiscriminate fashion, you may "write over" important parts of your program, or information that has been temporarily stored by the BASIC interpreter. The net effect is a "crash" of the computer system, in which your program and data will be lost or significantly altered. It is probably not a good idea to randomly POKE information into various addresses, until some specific guidelines are provided. Of course, you can use the PEEK command to examine the contents of a memory location whenever you wish, since this command will not alter the contents of an examined memory location. From the previous discussion of memory devices, you should realize that the POKE operation will have no effect on the read-only memory devices in the Apple.

#### **Memory Maps**

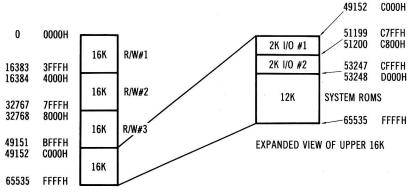

At this point it is a good idea to take a look at the "maps" of the memory addresses that are used by the Apple. A complete 64K memory map is shown in Fig. 1-3. For the sake of convenience, the memory addresses are provided in both decimal (base-10) and hexadecimal (base-16) notation. The hexadecimal numbers have a suffix of "H" to distinguish them from the decimal numbers.

The memory space for the Apple computer has been divided into four 16K blocks. Three of the blocks have been assigned for R/W memory, and most Apple computers have the R/W #1 block "filled" with read/write memory chips. The remaining R/W blocks may be used for future expansion of R/W memory, if this is required for particular applications. In most cases, we have found that 16K of R/W memory is sufficient. Add-on memory chip kits are available from many suppliers, and most Apple users can probably add the additional memory chips to their system without much difficulty.

The remaining 16K block of memory has been set aside for both ROM and I/O port addressing. The system ROMs for the Apple, which include the BASIC interpreter and the monitor programs, take up 12K of this space. The remaining 4K space is divided into two 2K spaces for I/O addressing and future expansion of the Apple. The I/O block with addresses C000H to C7FFH, inclusive, is the one of major importance for interfacing, since it has been specifically set aside for this purpose and it will never be used in Apple computer systems for any other purpose. Some of the addresses within this 2K block have been used by the Apple for controlling things such as the speaker, the keyboard, and the cassette recorder. The actual address

Fig. 1-3. 64K Memory map for the Apple computer.

19

assignments are shown in Table 1-3. We refer you to *Basic Programming Reference Manual*, and *Apple II Reference Manual*, for details on the actual use of these I/O addresses. These manuals are provided with the Apple II computer, and are also available from Apple Computer, Inc., 10260 Bandley Dr., Cupertino, CA 95014.

The remaining 2K block of memory, C800H-CFFFH, has been set aside for future expansion. You may use this space for additional read-only memory, if you have long programs that you wish to have readily available.

|                       | Address     |             |  |  |  |  |  |

|-----------------------|-------------|-------------|--|--|--|--|--|

| Function              | Decimal*    | Hexadecimal |  |  |  |  |  |

| Keyboard data         | 49152       | C000        |  |  |  |  |  |

| Clear-keyboard strobe | 49168       | C010        |  |  |  |  |  |

| Speaker               | 49200       | C030        |  |  |  |  |  |

| Cassette Output       | 49184       | C020        |  |  |  |  |  |

| Cassette Input        | 49256       | C060        |  |  |  |  |  |

| Flag Inputs           | 49249-49251 | C061-C063   |  |  |  |  |  |

| Analog Inputs         | 49252-49255 | C064–C067   |  |  |  |  |  |

| Analog Clear          | 49264       | C070        |  |  |  |  |  |

| Utility Strobe        | 49216       | C040        |  |  |  |  |  |

Table 1-3. Apple I/O Addresses and Their Uses

\*Only positive addresses given. To calculate negative addresses, just add —65536 to the decimal addresses provided.

In later sections of this book, the actual use of the I/O addresses will be described in detail. At this point, it is sufficient that you understand that a specific set of memory addresses has been set aside for your particular applications. You should also realize that the memory map shown in Fig. 1-3 is particular to the Apple computer. Other 6502-based computers will probably have different memory maps, with R/W memory, read-only memory, and I/O device addresses located in different areas of the map.

#### Software Commands and Interface Circuits

As you are probably aware by now, the PEEK and POKE instructions each cause some actions to take place, either at I/O devices or at memory locations, as a direct result of the use of the instruction. Instructions such as A=1.359 will cause some values to be stored in memory, but we do not know what memory locations the Apple has assigned to the variable "A" and we do not know how the value 1.359 has been stored. The PEEK and POKE instructions each cause a definite, known sequence of operations to take place, transferring data bytes, generating control signals, and transferring address information on the address-bus lines. These definite and reproducible actions allow us to use these commands to control I/O devices. We will now explore the actions that each of these software commands causes to take place.

The PEEK and POKE instructions operate in a very similar manner. In each, an address is specified, requiring 16 bits of information. During the execution of either instruction, the *address* information contained within the command is transferred to external devices on the address-bus lines, A15-A0. In this way, the I/O device address is available to all of the devices and circuits that are connected to these address lines, both memory and I/O devices.

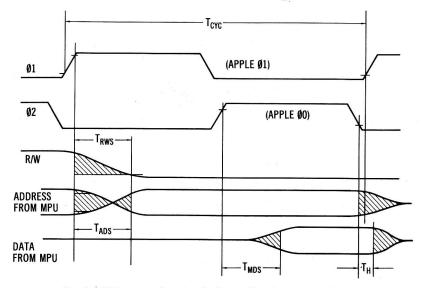

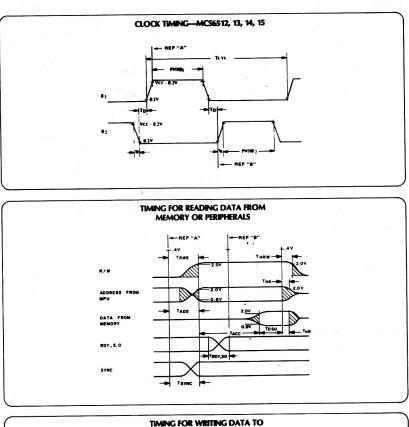

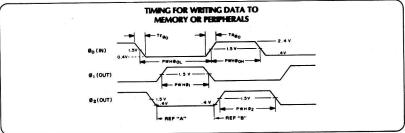

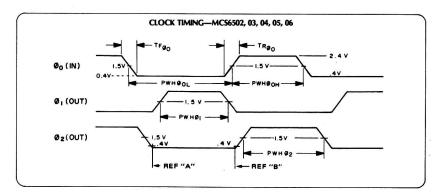

When a POKE instruction is used in a program, the data value is also output by the 6502 chip, but on the data-bus lines, D7-D0. Once the data bits and the address bits are "stable" or present on their respective buses in useable form, the 6502 asserts the READ/WRITE signal on the control bus. This synchronizes the acquisition of the data by the I/O device that was addressed. Of course, external circuitry is required to "capture" the data, as well as to identify the selected I/O device and synchronize it with the 6502-based system. A timing diagram for these signals, as they appear on the 6502 system, in this case the Apple, is shown in Fig. 1-4. Of course, the POKE command involves many assembly-language instructions, and the timing diagram shows what happens only during the time of the actual data transfer. At this point, we are only concerned with what the 6502 does during a POKE operation.

When a PEEK instruction is executed, the data is not contained in the instruction, but is acquired from an external I/O device. Only the address is specified. The 16-bit address is placed on the address-

Fig. 1-4. Write operation signal relationships. (See Appendix C.)

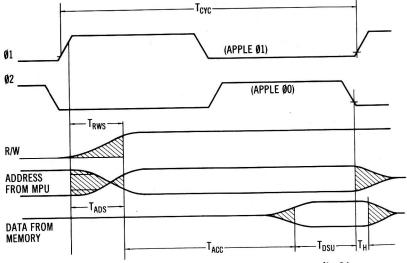

bus lines when the PEEK instruction is executed. When the address information is present, the corresponding I/O device must place its data on the data bus so that it may be accepted by the 6502 processor. During a read operation, the  $R/\overline{W}$  signal from the 6502 is a logic one. Additional circuitry is required here, too, to select the I/O device and to gate its data onto the data bus. A typical timing diagram for the PEEK command is shown in Fig. 1-5.

Fig. 1-5. Read operation signal relationships. (See Appendix C.)

We will describe shortly some of the circuits that are used for input and output ports. You have probably realized that while we have described an I/O port as one that can either receive data that is output by the microcomputer or transmit data that is input by the microcomputer, some I/O devices may actually contain a number of individual I/O ports. Industrial controllers, data storage devices (disks, cassettes), analog converters, and other I/O devices may have a number of I/O ports, since they may require more than eight bits of information from the computer and they may also need to transfer more than eight bits of information to the computer. In any case, transfers of data that contain more than eight bits always involve the transfer of multiple bytes to and from the computer and the individual 8-bit I/O ports. This is important to remember: information is always transferred eight bits at a time.

## Software Command–Data Transfer and Control

In most cases, the PEEK and POKE commands will be used to transfer 8-bit data values between the I/O devices or memory locations and the 6502 computer. As we noted previously, some data transfers will require more than eight bits of information, so multiple bytes are transferred, one byte at a time.

There are also cases in which the actual *value* of the data transferred is meaningless. The bits may be used to represent individual two-state conditions that are unrelated to the positional values of the bits. For example, a number of sensors could be connected to the Apple indicating conditions such as tank empty-or-full, heater on-oroff, value open-or-closed, and so on. A PEEK command could be used to input the status of these indicator bits, through an 8-bit input port. Thus, the value read from this input port might be 100, but the port is *sensing* eight individual on or off (logic one or logic zero) states, so the value of  $100_{10}$  is meaningless. The individual binary bits each represent the state of an individual sensor. In this case:

### $100_{10} = 01100100_2$

This indicates that three of the sensors are in the logic one state and five are in the logic zero state.

The POKE and PEEK commands can also be used in a similar manner to turn a device on or to turn a device off, based upon the state of the individual bits that have been sensed elsewhere in a control program. In fact, many of the I/O addresses used by the Apple are assigned to simple on/off devices such as the speaker. Thus, a simple command:

A = PEEK(49200)

will generate a "blip" on the speaker in the Apple. You should understand that the variable, A, is a "dummy," and its final value is not important, since the net effect of the simple BASIC statement is to pulse the speaker once. The speaker control command may be used in a loop to generate a low buzz from the speaker. This is shown in Example 1-4.

#### Example 1-4. A Simple Speaker Control Program

10 A = PEEK(49200) 20 GOTO 10

The important point to remember here is that the PEEK and POKE instructions are not limited simply to controlling the transfer of information on the data bus. They may also be used for specific control functions, such as pulsing a counter, turning on a pump, or tilting a solar collector.

#### Assembly Language and BASIC

The BASIC-language programs that you write on your Apple computer bear very little relationship to the actual instructions that the 6502 microprocessor chip can actually execute. Each of your BASIC statements and commands is *interpreted* by the BASIC *interpreter* resident within the Apple computer. A programming manual for the 6502 chip, itself, would bear little relationship to the Apple software manual. The commands are very different.

The 6502 does not have a PRINT command, so it would not perform the following operation:

PRINT "THIS LOOKS LIKE FUN"

The BASIC interpreter determines that a PRINT operation is to take place and it then executes a series of assembly language program instructions that actually place the codes for the alphabetical characters in the display memory to spell out, "THIS LOOKS LIKE FUN." The assembly language steps consist of logic ones and zeros that cause the necessary internal and external 6502 operations to take place to transfer the message portion of the PRINT command to the display memory.

While we will not use assembly language programming to any extent in this book, you should be aware that it is the "base" computer language that causes the Apple to operate the way that it does.

The PEEK and POKE commands each cause many, many assembly language commands to be executed to produce the overall effect of data transfer. Since these BASIC language instructions must be interpreted, even when used one right after another, or in a loop, the *interpretation* software process can be slow. Two programs are shown in Example 1-5, both of which control the speaker in the Apple. Each series of program steps does the same thing; generating a tone on the speaker. Simply by listening to the differences in the two tones produced, you will be able to appreciate the difference in the speeds of execution of these programs.

#### Example 1-5. Comparison of Assembly Language and BASIC Programs for Speaker Control

|    | Basic Program   | am Assemb |           |  |

|----|-----------------|-----------|-----------|--|

| 10 | A = PEEK(49200) | GO        | LDY #\$CO |  |

| 20 | GOTO 10         | LOOP      | LDA #\$OC |  |

|    |                 |           | JSR WAIT  |  |

|    |                 |           | LDA SPKR  |  |

|    |                 |           | DEY       |  |

|    |                 |           | BNE LOOP  |  |

|    |                 |           | JMP GO    |  |

The assembly language program generates a pleasing, even tone, while the BASIC program generates a low rumble. The assembly language program is similar to the one used by the Apple Monitor program where the internal WAIT subroutine has been used to generate a delay.

In some cases, assembly language programs have a *five-hundred* to one advantage over BASIC programs, although the BASIC pro-

grams are probably easier to write and debug. Assembly language programming is generally not recommended for the novice.

We will be mentioning assembly language programming very little, concentrating on the use of BASIC language programming instead. For further information on 6502 assembly language programming, we recommend 6502 Software Design and Programming and Interfacing the 6502, With Experiments (Howard W. Sams & Co., Inc., Indianapolis, IN 46268).

#### **Binary and Decimal Numbering**

Likewise, the data values transferred to and from the computer by the PEEK and POKE commands are also specified or acquired as 8-bit binary values, since the data bus is only eight bits "wide." The 8-bit data bus is a function of the data processing capability within the 6502 chip. It is *not* a function of the Apple. Thus, we are limited to 8-bit data transfers. Is this a great limitation? Generally not. In spite of it, the Apple can process a great deal of information, and, as you will see later, it is easy to interface to I/O devices.

One final note on addresses is necessary before leaving this chapter. The BASIC interpreter in the Apple computer has been set up to handle both *negative and positive* addresses. This does not mean that there are actually negative addresses in the computer. Can you imagine negative street numbers? The negative numbers are simple due to the way in which the *binary* equivalents of the addresses are stored in the Apple. Thus, the address for the speaker, 49200, is equivalent to -16336. To avoid confusion, we strongly recommend the use of the positive addresses. You can easily convert between negative and positive addresses simply by (a) adding 65536 to a negative address to yield the positive equivalent, or (b) by subtracting 65536 from the positive address to yield the negative equivalent. Both addresses, 49200 and -16336, generate the same 16-bit address, but we think that you will agree that negative addresses can seem a bit abstract and confusing.

# **Apple Interfacing**

At this point, you are probably wondering:

- How does the Apple actually transfer information to I/O devices?

- How are the I/O devices actually synchronized to the operation of the computer?

- How are individual I/O devices selected or identified?

- How do I/O devices place their data on the data bus and how do they actually receive it from the data bus?

These are important questions, since the answers to them will provide the basis for your understanding of microcomputer interfacing. We will be answering these questions in this and other chapters. We will also provide some experiments that will reinforce the concepts through hands-on experience.

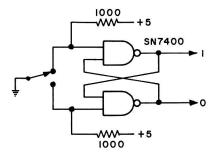

A few examples of digital circuits will be provided in this chapter. We have assumed that you can "read" and interpret a logic circuit diagram, and that you are familiar with the more common SN7400series transistor-transistor logic (TTL) circuits

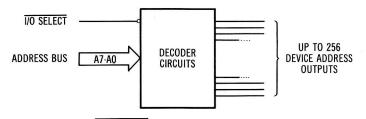

#### I/O DEVICE ADDRESS DECODING

Before we can discuss the actual transfer of information between I/O devices and the computer, we must first understand the circuitry and the signals that are used to identify or address the individual I/O devices. There are many schemes that may be used and we will examine several of them. It is impossible to show every possible scheme for addressing I/O devices, since modifications will be made to suit special needs.

When the Apple computer is programmed to perform a data transfer using either of the general-purpose I/O commands, PEEK or POKE, certain signals are generated by the 6502 processor to synchronize the flow of data. At this point, our main concern is the use of the address bus lines. These are the 16 lines that address individual memory locations and I/O devices. You should recall that the PEEK and POKE instructions each contain decimal address information that is used to identify the addressed memory location or I/O device. Of course, the Apple computer has no way of distinguishing between a memory location and an I/O port.

#### **DEVICE ADDRESSING**

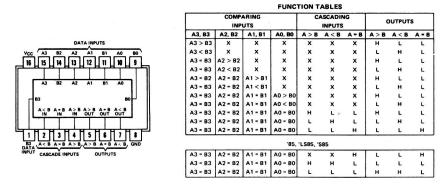

Each I/O device that is to be used with the computer must be able to recognize its own device address. Since the PEEK and POKE commands use 16-bit addresses, each I/O device must monitor these 16 address lines, A15-A0, for the occurrence of its address. There are three basic schemes that may be used by I/O device circuits to accomplish the monitoring for a specific address. These are:

- Gating-detecting a specific combination of logic signals.

- Decoding-a more flexible gating scheme in which many addresses may be detected.

- Comparing-comparing a preset or known address with the address-bus signals until a match occurs.

Combinations of these three techniques are possible and there are probably many variations that are possible. We will describe examples of each of the three basic address decoding schemes.

#### **Using Gates for Address Decoding**

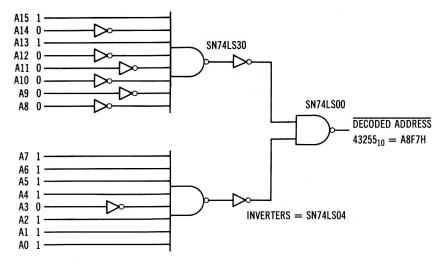

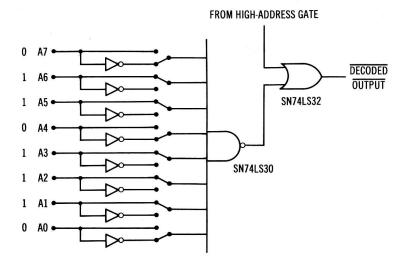

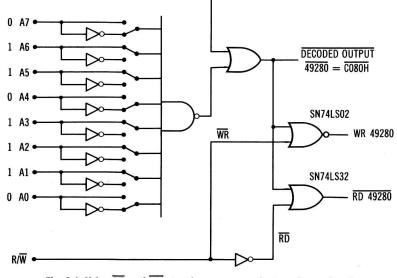

In the scheme for decoding device addresses in which individual gates are used, the address must be known so that the gates can be properly configured. In this example, we will use the device address  $1010100011110111_2$  or  $43255_{10}$ . Since the binary notation is long, and somewhat cumbersome, you might feel more comfortable with the hexadecimal equivalent, A8F7H. Since NAND/AND gates are the predominant type of gating logic available, we will use these types of circuits in our logic.

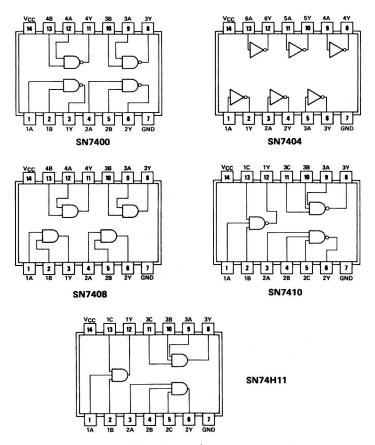

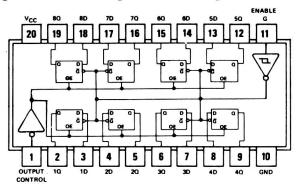

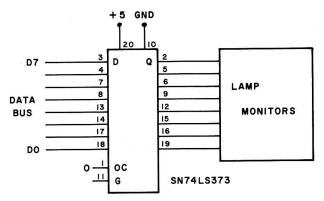

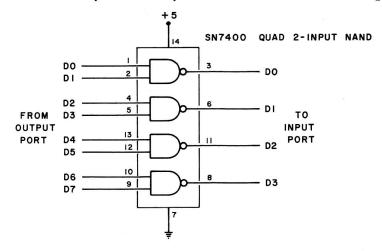

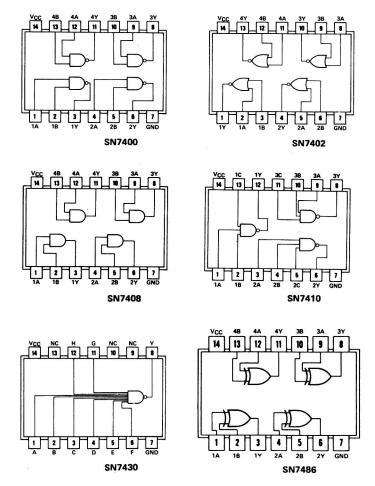

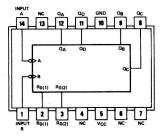

To refresh your memory, the pin configurations for several types of AND/NAND gates are shown in Fig. 2-1, with the generalized truth table for a two-input AND gate and an equivalent NAND gate shown in Table 2-1. Since inverters such as the SN7404 are often found in device addressing circuits, a pin configuration for this chip has been included in Fig. 2-1. The truth tables in Table 2-1 also show the function of an inverter. In all cases, the logic one state is the higher volt-

Fig. 2-1. Inverter and various AND/NAND gate pin configurations.

age (+2.8 to +5 volts) and the logic zero state is the lower voltage (0.0 to 0.8 volt). The NAND gate functions are available with 2, 3, 4, 8, and 13 inputs, while the AND gates are available with 2, 3, or 4 inputs.

Since the unique output state, logic one for an AND gate and logic zero for a NAND gate, occurs only when *all* of the inputs to an AND or a NAND gate are all logic ones, we will have to configure the binary address 1010100011110111<sub>2</sub> so that it generated 16 logic ones at the input to the AND or NAND gate, when it is present on the 16-bit address bus. You have probably realized that there are no 16-input AND or NAND gates available commercially, so some other configuration must be used instead. It is very easy to use a separate 8-input NAND gate to detect a pattern of binary address bits on the high-address bus (A15-A8), and another 8-input NAND gate to detect a pattern of binary bits on the low-address bus (A7-A0). Simple inverter func-

| AND Gate |     | NAND Gate |     | Inverter |        |       |        |

|----------|-----|-----------|-----|----------|--------|-------|--------|

| Inp      | uts | Output    | Inp | outs     | Output | Input | Output |

| A        | в   | Q         | Α   | В        | Q      | A     | Q      |

| 0        | 0   | 0         | 0   | 0        | 1      | 0     | 1      |

| 0        | 1   | 0         | 0   | 1        | 1      | 1     | 0      |

| 1        | 0   | 0         | 1   | 0        | 1      |       |        |

| 1        | 1   | 1         | 1   | 1        | 0      |       |        |

Table 2-1. Truth Tables for a Two-Input AND Gate, NAND Gate and an Inverter

tions are used to invert the logic zero address bits so that they apply logic ones to their corresponding gate inputs, as shown in Fig. 2-2. In this circuit, two inverters and a NAND gate have been used to combine the output from each of the 8-input NAND gates, so that the output of the circuit will be a logic zero only when the *complete* pattern of 16 bits, 1010100011110111<sub>2</sub>, is detected on the 16-bit address bus.

Fig. 2-2. Gating circuit used to decode address 43255 or A8F7H.

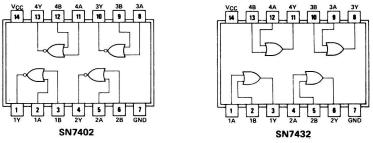

One of the disadvantages of this circuit is that some of the address signals must go through four gates before reaching the decoded address output from the 2-input NAND gate. Since each gate delays the signal slightly, this might cause some timing problems in the circuit. Actually, the time delays are fairly minor, and we will ignore them for now. The delay can be reduced somewhat by using a NOR or OR gate in the circuit to combine the outputs from the two 8-input NAND gates. This is good design practice. NOR and OR gates are readily available and are used quite extensively in computer interfacing. A

Fig. 2-3. Typical NOR and OR gate IC pin configurations.

typical NOR and OR gate are shown in Fig. 2-3, with the corresponding truth tables provided in Table 2-2.

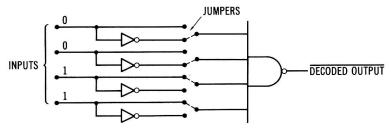

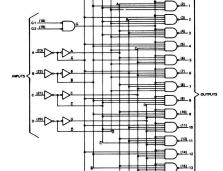

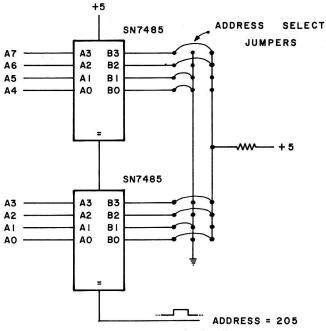

While the gating scheme shown in Fig. 2-2 is effective in decoding a single address, and relatively inexpensive, it is inflexible. A more flexible approach is shown in Fig. 2-4. This circuit illustrates the use of a gating scheme in which inverters may be used to invert individual address bits, as required. The bits may also be used without inversion. The jumpers allow the device address to be preset, as illustrated in Fig. 2-5. In this circuit, only the low-address bus gating has been shown, for clarity. A duplicate gating circuit is required for the high-address bus lines. In this type of a gating circuit, any one of the 65536 possible addresses may be selected, but only one at a time.

The programmable gating circuit provides broad flexibility, in that addresses are easily changed to meet specific requirements for an interface, but such a circuit can select only a single address, and this is a severe limitation. When several I/O devices are located on the same circuit board, each will require its own address gating circuit. This limitation can be overcome with other addressing schemes.

Unfortunately, the gating schemes that we have shown are not all that is required to uniquely address and control an I/O device. You should recall from the discussion of the READ/WRITE (R/W)signal in the previous chapter, that the R/W signal is used to synchronize the flow of information to and from the computer. The I/O devices must also use this control signal, if they are to use the data bus properly. In many interfaces that are designed for 6502-based com-

| 1   | NOR | OR Gate OR Gate |     | Gate |        |  |

|-----|-----|-----------------|-----|------|--------|--|

| Inp | uts | Output          | Inp | uts  | Output |  |

| Α   | В   | Q               | A   | В    | Q      |  |

| 0   | 0   | 1               | 0   | 0    | 0      |  |

| 0   | 1   | 0               | 0   | 1    | 1      |  |

| 1   | 0   | 0               | 1   | 0    | 1      |  |

| 1   | 1   | 0               | 1   | 1    | 1      |  |

Table 2-2. Truth Tables for a Two-Input NOR Gate and OR Gate

Fig. 2-4. A simple 4-input gate that can be programmed for 1's and 0's.

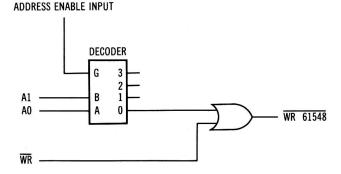

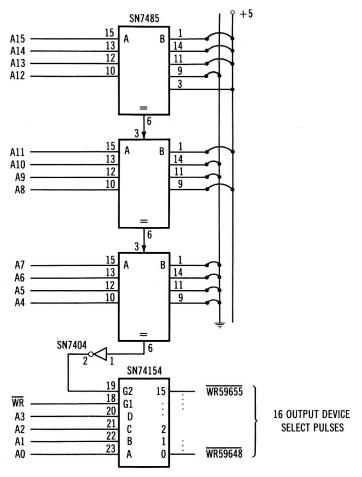

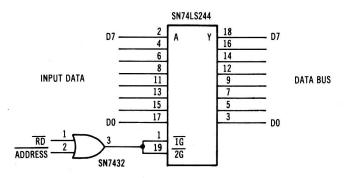

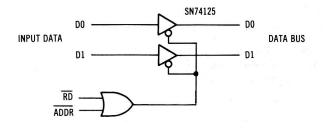

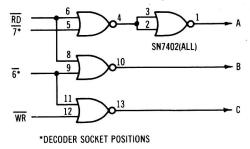

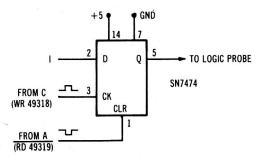

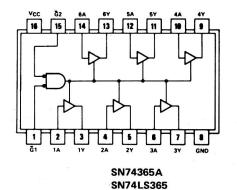

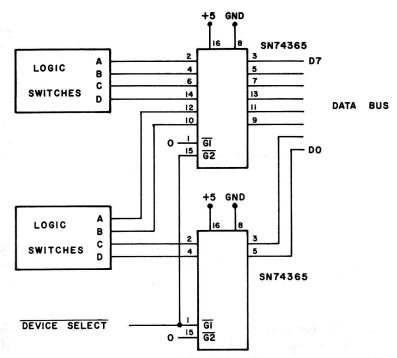

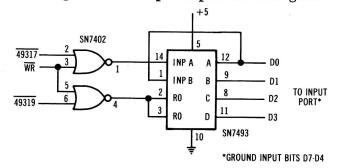

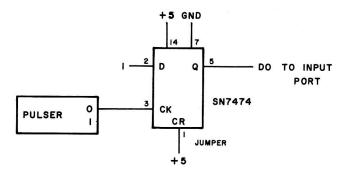

puter systems, the  $R/\overline{W}$  line is used to provide the logic-zero write pulse, with the  $R/\overline{W}$  signal being *inverted* to generate a separate read pulse. The two resulting control signals, WRITE (WR) and READ (RD), are easy to use in interface circuits, since they are active in the logic zero state. The use of these signals is shown in Fig. 2-6. In this circuit, the output from the 16-bit gating circuit is combined with  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  to provide two signals for I/O port control. These two control signals are a combination of the decoded address and the WRITE pulse, and a combination of the decoded address and the  $\overline{\text{READ}}$  pulse. The resulting pulse from each gate is called an address select pulse, or a device select pulse. More generally, a decoded address is gated with a function pulse ( $\overline{RD}$  or  $\overline{WR}$ ) to generate a device select pulse. In the circuit diagram shown in Fig. 2-6, the RD 49280 pulse could be used to control an input port, while the WR 49280 pulse could be used to control an output port. Note that the notation for the WR 49280 pulse does not have a "bar" over it.

Fig. 2-5. Programmable gate used for device address decoding. (High address section is equivalent.)

FROM HIGH-ADDRESS GATE

Fig. 2-6. Using RD and WR signals to generate device select pulses for device synchronization.

This means that the pulse is active in the logic one state, while the  $\overline{\text{RD}}$  49280 pulse is active in the logic zero state. In this example, it is quite proper to note the address on the I/O ports by using a hexadecimal value, for example,  $\overline{\text{RD}}$  C080H.

Before going further, you should be sure that you understand that a reading operation involves reading information into the computer from an input port, while a writing operation involves the transfer of information from the computer to an external device. It is also quite proper and useful to use one address to control an input port and an output port. Since the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  pulses cannot be coincident, there is no conflict between an input port and an output port that have been assigned the same address. You cannot assign two input ports the same address, and you should not assign two output ports the same address. In fact, you may find that even though an input port and an output port have been assigned the same address, they may be unrelated as to their function, and may be used on separate interface circuits.

The concepts and the basic circuits that have been developed in this section are very important and they will be carried forward to other sections and chapters. It is important that you understand the use of the signals that have been discussed to select devices. We have not yet discussed what these input and output devices are, or how they work, but we shall discuss this in the next chapter.

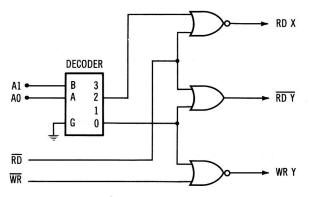

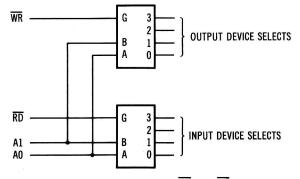

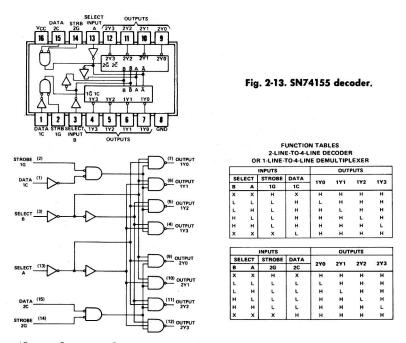

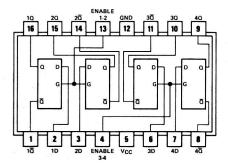

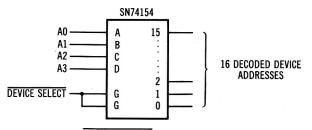

#### **Using Decoders**

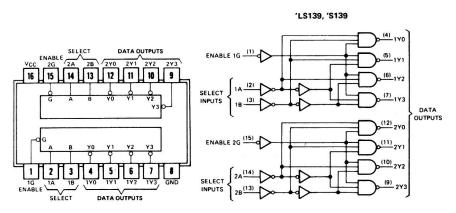

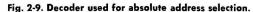

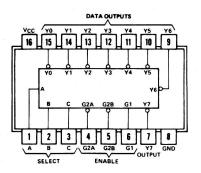

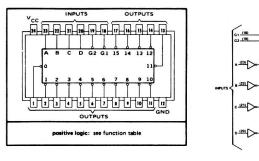

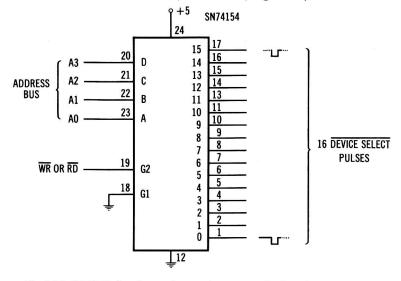

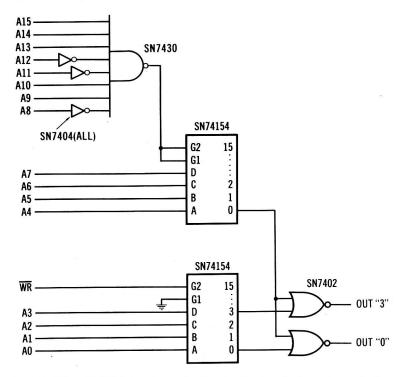

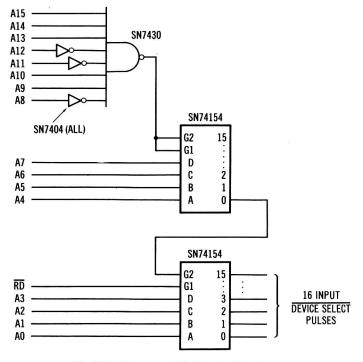

In many cases, it is easier to use *decoder* circuits in place of the gate address detecting circuits, and, in some cases, in place of the NOR-gate device select circuits, too. Why are decoders so useful? Perhaps it is best to take a look at several types of decoders to see what they look like and how they operate. As you examine the decoder circuits, keep in mind that they are simply collections of gates that have been "integrated" into an easy-to-use decoder circuit.

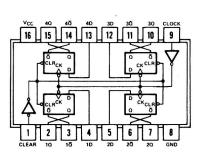

Decoder circuits are generally specified as x-line to y-line decoders, where x represents the number of binary inputs, say four inputs, and where y represents the number of possible outputs, or the number of different binary states present on the x inputs. Thus, for the four inputs, there would be 16 possible outputs, creating a 4-line to 16-line decoder or a 4- to 16-line decoder. This is, in fact, a real decoder circuit, as you will see.

Each of the binary inputs has two states, a logic one and a logic zero. These inputs are independent of one another. The outputs are also binary, in the sense that they have two possible values, but they are *not independent*. There will only be *one* unique output from the decoder, representing the value or "weight" present at the binary inputs. In most cases, the unique output state is a logic zero, with the other outputs in their logic one state.

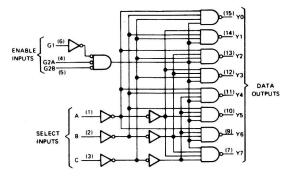

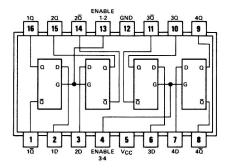

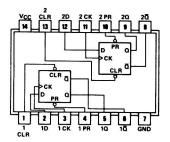

A typical decoder integrated circuit is the SN74LS139. This integrated circuit actually contains two independent two-line to fourline decoders, as shown in Fig. 2-7.

The truth table for the SN74LS139 is shown in Table 2-3.

Of course, the truth table applies to both of the decoders within the SN74LS139 integrated-circuit package, or "chip." Most decoder circuits incorporate an enabling input, so that the decoder may be

Fig. 2-7. SN74LS139 decoder chip schematic diagram and pin configuration.

|     | Outputs          |                          |                                  |  |

|-----|------------------|--------------------------|----------------------------------|--|

|     | YI               | ¥2                       | Y3                               |  |

| YO  |                  |                          |                                  |  |

| н   | н                | н                        | н                                |  |

| L L | н                | н                        | н                                |  |

| н   | L                | н                        | н                                |  |

| н   | н                | L                        | н                                |  |

| н   | н                | н                        | L                                |  |

|     | H<br>L<br>H<br>H | н н<br>L н<br>н L<br>н н | H H H<br>L H H<br>H L H<br>H H L |  |

Table 2-3. Truth Table for an SN74LS139 Decoder

turned on or turned off by one logic input. This is the function of the ENABLE or "G" input on each of the decoders in the SN74LS139. Note that when the "G" input is a logic one, all of the outputs are forced into the logic one state, regardless of the states of the A and B inputs. This allows the decoder to be gated on or off. In the off state, the power is not removed, but the outputs are all forced into the logic one state.

Let us now examine a simple, rather trivial, example of the use of a two-line to four-line decoder for device address decoding. We will assume that we only have a few I/O devices, so that the decoders in the SN74LS139 decoder package can handle our needs. A typical decoder circuit is shown in Fig. 2-8. In this circuit, only two address bits have been decoded, the rest have been ignored. Note that the enable input has been grounded so that the outputs of the decoder will operate properly. The added NOR and OR gates generate the actual device select pulses.

The device select signals have been noted as RD X, RD Y, and WR Y, since there is no *specific* address that will actuate each. Addresses 01010101 00000010, 00011101 11110110 and 00000000 11111110 will all cause the RD X device select pulse to be generated, if they are

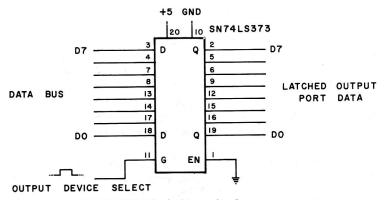

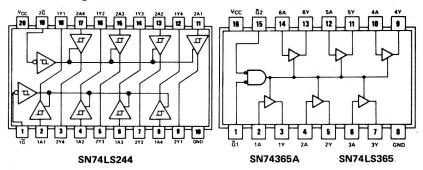

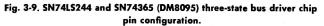

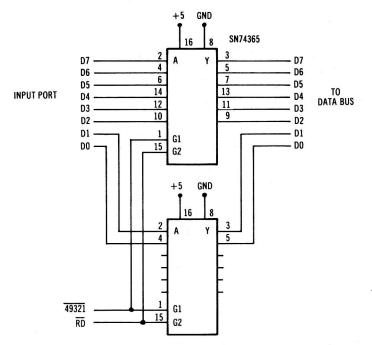

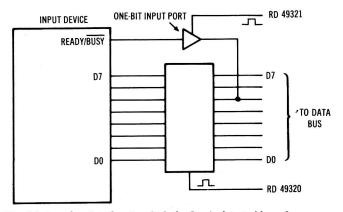

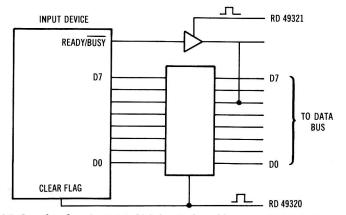

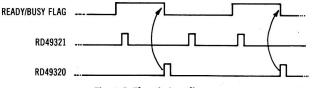

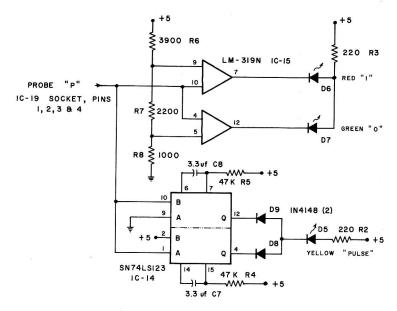

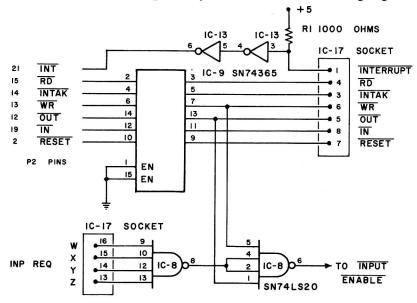

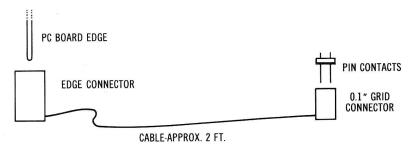

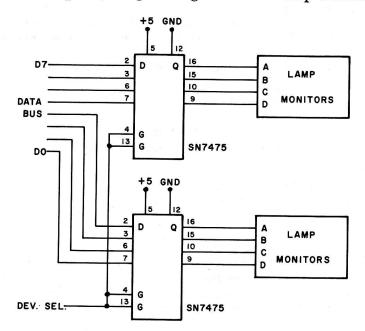

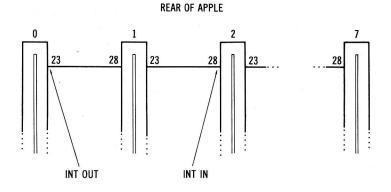

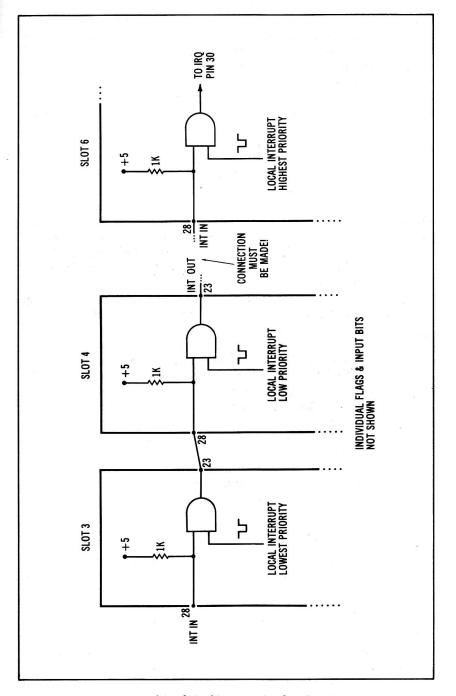

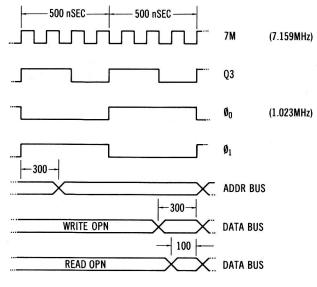

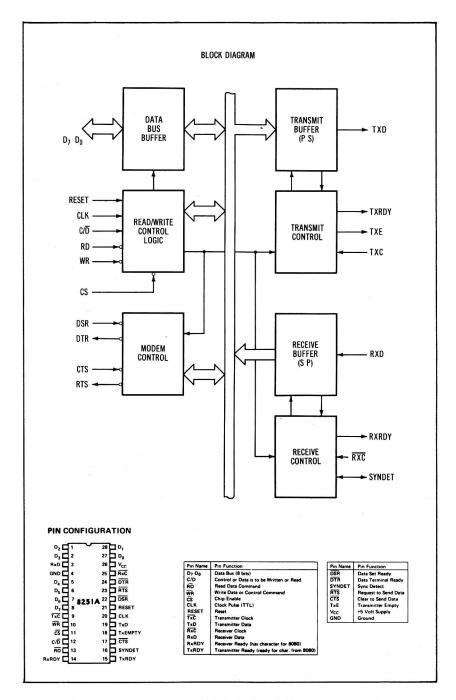

Fig. 2-8. 2-Line-to-4-line decoder used for device addressing.