# Does Anybody Really Know What Time it is?

Add a real time, noninterruptable hardware clock/calendar to your 6502 system using a new clock chip and you will be as close to knowing as anyone can be.

A hardware real-time clock has several advantages over a software real-time clock. First, keeping time does not require interrupt driver software. thereby saving machine time overhead and RAM space. Next, the circuit described here can generate its own interrupts to the microprocessor if regularly spaced interrupts are needed. Finally, and perhaps most significant is that being non-interruptable with its battery backup, the time only has to be set when starting up the first time. Neither turning off the microprocessor system nor power outages affect the keeping of time.

### The MSM5832

The MSMS832 from OKI Semiconductor is a CMOS clock/calendar chip made especially for bus-oriented microprocessor applications. Due to its special design, it offers many advantages over other types of conventional clock circuits when used with a microprocessor as a non-interruptable clock/calendar.

The MSM5832 keeps track of seconds, minutes, hours, day of the week, date, month, and year. Data is read and written by using a four bit bi-directional bus, when addressed by a four bit address bus. Table I shows the function of each address. Notice that in

| ADDRESS |   |   |    | INTERNAL |   | DATA I/O |   | DATA |        |                                                          |  |

|---------|---|---|----|----------|---|----------|---|------|--------|----------------------------------------------------------|--|

| 40      |   |   | λЗ | COUNTER  |   | Dl       |   |      | LIMITS | NOTES                                                    |  |

| 0       | 0 | 0 | 0  | s 1      | • | ٠        | • | •    | 0-9    | S1 or S10 reset to<br>zero whenever write                |  |

| 1       | 0 | 0 | 0  | S 10     |   | ٠        | ٠ |      | 0-5    | is executed                                              |  |

| 0       | 1 | 0 | 0  | MI 1     | • | ٠        | ٠ | ٠    | 0-9    |                                                          |  |

| 1       | 1 | 0 | 0  | MI 10    | • | ٠        | ٠ |      | 0-5    |                                                          |  |

| 0       | 0 | 1 | 0  | н 1      | • | •        |   |      | 0-9    |                                                          |  |

| 1       | 0 | 1 | 0  | н 10     |   | •        | t | 1    | 0-1    | D2="1",PM D3="1",24 Hour<br>D2="0",AM D3="0",12 Hour     |  |

| 0       | 1 | 1 | 0  | w        | • |          | • |      | 0-6    |                                                          |  |

| 1       | 1 | 1 | 0  | D 1      |   | ٠        | ٠ |      | 0-9    |                                                          |  |

| 0       | 0 | 0 | 1  | D 10     |   | ٠        | + |      | 0-3    | D2="0",29 days in month 2(2<br>D2="0",29 days in month 2 |  |

| 1       | 0 | 0 | 1  | MO 1     | • | •        | ٠ | •    | 0-9    |                                                          |  |

| 0       | 1 | 0 | 1  | MO 10    | • |          |   |      | 0-1    |                                                          |  |

| 1       | 1 | 0 | 1  | Y 1      | • | ٠        | • | ٠    | 0-9    |                                                          |  |

| 0       | 0 | 1 | 1  | Y 10     |   | •        | ٠ |      | 0-9    |                                                          |  |

(1) \* Data valid as "0" or "1". Blank does not exist(unrecognized during WRITE and held at "0" during READ).

f Data bits used for AM/PM, 12/24 Hour and leap year.

(2) If D2 previously set to "1", upon completion of nonth 2 day 29. D2 will be internally reset to "0"

# Table 1: Functions

|   | CONDITIONS | OUTPUT | REFERENCE<br>FREQUENCY | PULSE<br>WIDTH |

|---|------------|--------|------------------------|----------------|

|   | HOLD = L   | D0(1)  | 1024 Hz                | duty 50%       |

|   | READ = H   | Dl     | 1 Hz                   | 122.1 us       |

|   | CS = H     | D2     | 1/60 Hz                | 122.1 us       |

|   | A0-A3 = H  | D3     | 1/3600 Hz              | 122.1 us       |

| 1 |            |        |                        |                |

1024 Hz signal at DO not dependent on HOLD input level.

Table 2: Reference Signal Outputs

addition to being able to program through software either a 12 or 24 hour format, leap years are handled quite easily. Lean years are controlled by hit D2 of address 8. When set, it gives the second month of the year a 29th day, and after the 29th day has elansed, the bit is automatically cleared. The bit may be set any time after the second month of the previous year, and before the end of the second month of the leap vear.

Another feature is a manual +30 second correction input. Perhaps the most unique and useful feature is the HOLD control which allows read/write operations to occur with the counters being held static, without disturbing the accuracy of the real time. Additionaly, four different interrupt outputs are available to the microprocessor, as shown in table 2. Finally, the chip will operate on a battery back up as low as 2.2V with a power dissipation of less than 90uW. making long term backup quite attractive and economical.

### Functions

The functions of the clock/calendar are best described on an individual hasis as follows

### Oscillator (XT.XT)

A 32.768KHz(215) crystal is connected to an internal, stable oscillator to form an accurate time base. The two parallel capacitors, one of which is a trimmer, allow the oscillator to be tuned quite precisely.

# A0-A3

These are the address inputs which are used to select the internal counters to be set or read on a read or write operation.

# DO-D3

These are data inputs or outputs, depending on whether a read or write operation is being done. They are tristate bi-directional ports controlled by the READ and WRITE controls.

# Chip Select

This determines whether the inputs and outputs are active or inactive. Connecting the CS to Vcc activates the inputs and outputs, while connection to ground disables them. In the circuit in figure 1, the CS is permanently con-nected to +5V from the microprocessor system for battery backup configuration. When the main system is turned off, this disables all

Set HOLD high

150 µsec delay

Set WRITE high

Output address

and data

Clear WRITE

Done

Clear HOLD

END

YES

functions except the counting circuits. allowing very low power consumption while still keeping time by the battery backup.

# Hold

OFA7-

OPAA-A9 3F

OFAC-8D 03 A8

OFAF-A9 OC

OPPI-8D OC A8

OFC4-48

OFC5-09 10

OFC7-8D 01 A8

OPCA-FA

OFCR-

OFCC-EA AD 00 A8 OPCD-

OPPO-20 00

OFD2-

OFD4-CA

OFD5-

OFD7-49 OF

OFD9-8D 0C A8

OFDC-60

OFF7-CA 10 ED

OFFR-

OFFA-A9 OE

OFFC-8D OC A8

OFFF-60

95 89

10 ED

A high on this line keeps the seconds counter from being incremented by the 1Hz clock output. After the initial set up time (150 microseconds), all counters will be in a static state, allowing error-free read and

20 86 8B SETUP

write operations as long as the HOLD time is less than one second. Other clock circuits do not have this feature. and operations have to be done twice and compared to assure no error has heen made

Consider the following example with a conventional clock circuit. Suppose you are reading a time of 12 hours and 59 minutes. If the seconds count should be 59, and after the hours (and before the minutes) are read, the seconds counter clears and sends a carry pulse, the time is then 13 hours, 0 minutes and 0 seconds. But the read operation has resulted in 12 hours, 0 minutes and 0 seconds—a full hour off. It is for this reason that with conventional clock circuits two reads have to he made to insure proper information has been received

# Read

This input, when taken to Vcc, signals a read operation.

### Write

This input, when taken to Vcc. signals a write or set operation. This method of being able to directly set the time is far easier to use than conventional circuits in which pulses must be directed to either a fast set or slow set input, and the clock must read between pulses until the desired time has been

+30 Adinst Momentarily taking this input to Vcc will reset the seconds count to zero. If the seconds count was 30 or more before this action, a carry is sent to the minutes counter. If less than 30, the minutes count remains unchanged. This means that keeping the time accurate is a very simple matter. If the switch in figure 1 is momentarily pressed at the start of a minute, this will automatically reset the time to the correct value as long as the clock is less

Test This input allows testing of the operation of the clock. Pulses to this input will directly clock the \$1, MI10, W. D1, or Y counters, depending on which one is addressed by A0-A3.

than 30 seconds either fast or slow.

# Reference Signal Outputs

Outputs are available from D0-D3 when READ, CS, and A0-A3 are at Vcc. These can be used as interrupts to the microprocessor. Table 2 presents the conditions for these signals.

### Operation

Figures 2 and 3 present the flow diagrams for read and write operations. Although self-explanatory, there are several aspects of the operations which should be emphasized, especially for applications other than the specified one given in this article. First, the HOLD control must always be given at least 150 microseconds set up time, and must be used for WRITE opera-

tions. Next, since the read access time

# Listing 1: Machine Language Routines

Machine language routines for MSM5832 Clock/Calendar circuit Randy Sebra July, 1980

ACCESS EQ 38882 Un-write protect system RAM ORB EO \$A800 Output register B TORA ED \$A801 Input/output register A DORR ED \$A802 Data direction register B CA 003 Data direction register A DDRA EO PCR EO SAROC Peripheral Control Register SOFA7 Start of routines

Routine to configure Port B and ACCESS

set ROLD high

JSR

t.Da #3P

STA DDDS

LDA #OC

STA PCR

ROLCOP TXA

ORA **#10**

STA

NOR

NOP

LDA ORB

AND #0F

DEX

Delay 150 microsec for AO 25 OPPA-#25 DELAY OFR6-88 HOLD time set up DELAY OFB7-DO FD DNE OFB9-60 275 Return Read routine OFBA-20 A7 OF READ JSR SETUP Set up HOLD A9 00 I.DA #00 Configure PBO-PB3 as data OFRD-8D 02 A8 STA DDSS inputs for read OFRF-Initial address OFC2-A2 0C T.DY #OC

Transfer to accumulator and combine with READ high IORA Issue RFAD Small delay for read access time Read data Mask off high 4 bits Store to Page Zero E9,X Decrement address PDT-OOR Loop until through Then set HOLD low

by CA2 high

Return

Remove write protect Set up PAO-PAS as outputs

for address and control Set CA2 low for high

input to HOLD

### BPL f.DA STA RTS Write routine

DEX

BPL

LDA #OE

STA PCR

| OPDD- | 20 | A7  | OF  | WRITE  | JSR | SETUP | Set up HOLD            |

|-------|----|-----|-----|--------|-----|-------|------------------------|

| OFEO- | A9 | OF  |     |        | LDA | #OP   | Configure PBO-PB3 as   |

| OFE2- | 8D | 02  | AR  |        | STA | DORB  | data outputs for write |

| OPES- |    | OC. |     |        | LDX | #0C   | Set initial address    |

| OFE7- | B5 | E9  |     | WRLOOP | LDA | 29.X  | and fetch data         |

| OFE9- | 80 | 00  | A8  |        | STA | ORB   | Write data             |

| OFEC- | 84 |     |     |        | TXA |       | Combine address with   |

| OFED- | 09 | 20  |     |        | ORA | #20   | WRITE high and         |

| OPEF- |    | 01  | AR  |        | STA | IORA  | issue write            |

| OFF2- |    | OF  |     |        | AND | 405   | Toggle WRITE control   |

| Opp.  |    | 0.1 | - 0 |        | oma | YORK  |                        |

#OR

DCD

Decrement address WRLOOP Loop until through Set CA2 high for low on HOLD

Return

of the chip may be as long a 6 microseconds, a delay must be built in before reading data. Additionally, notice that although the READ control may be held high for as many read operations as desired, the WRITE control must be pulsed between each write operation.

# Interfacing

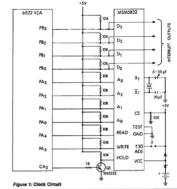

There are many ways which the MSMSS32 can be interfaced with a 6502 or other microprocessor. The only requirement is eleven I/O lines, with four being bi-directional. For myself, the most convenient method was through the use of the #2 6522 VIA on figuration. If you do not have a 6522 warlable on your system, it is a relatively simple matter to add one. See "Am Additional I/O linerface for the Warland of the

Transistor O1 in figure 1 at the HOLD pin is used to invert the CA2 input to HOLD. The reason for this is as follows. On power up and reset, all registers in the 6522 are cleared. This causes all I/O lines to be configured as inputs with a high voltage on the pins. and the HOLD would be held high. When using a hattery back up, this would cause the clock to stop until the HOLD is pulled low, since the hold time would always be longer than one second. With the HOLD being control led separately by the CA2 output and inverted, this will always keep HOLD low unless intentionally taken high by software

For battery back up, the chip select is connected to +5V from the 6502 bus, which disables all inputs and outputs when the system is off and the clock is on back up. The batteries used here are dry cells and the setup is a rather simple battery back up. A more elaborate setup could be used with NI-CADs and with the +5V trickle charging the batteries when the system is up. This could give many years of continuous operation before having to replace batteries. The battery life in both cases, of course, is a function of how frequently (or infrequently) the main system is used.

## Listing 2: Basic Routine and Sample Run

```

100 REM

110 REM

MEMBERS OF DOX /CAN PURSE

120 REM

SET/READ PROGRAM

BANDY SERRA JULY 1980

140 REM

150 DEF PHS(X)-INT(X/10)

160 DEF PNT(Y)=Y-FNS(Y)*10

170 INPUT"SET(S) OR READ(R) ? ":I$

180 IF IS .. THEN 430

190 REM

200 REM

GET INPUT AND STORE INTO LOCATIONS $E9-$P5

210 REM

220 INDUT*MONTH.DAY.YEAR(2 DIGITS) 7 ":M2.D.Y

230 POKE 245 PNS(Y

240 POKE 244, FNT(Y)

250 POKE 243, FNS(M2)

260 POKE 242, PNT(H2)

270 POKE 241. FMS(D)

280 POKE 240, PNT(D)

290 INPUT DAY OF THE WEEK(1-7) ? ":W

300 POKE 239, N-1

310 INDUTTHOURS MINETES(24 HOUR TIME) ? ": H. H.

320 POKE 238. PMS(H)+8

330 POKE 230, PMS(H)

340 POKE 236, PMS(H)

350 POKE 235, FNT(N)

360 REM

370 REM

CALL MACHINE LANGUAGE WRITE ROUTINE

380 PTM

390 S-USR(& "OFDD" .0)

400 REM

410 27

CALL MACHINE LANGUAGE READ ROUTINE

420 PFW

430 R-USR(4"0PBA".0)

440 DIM D$(6),M$(11)

450 DEF PNR(I)=PREX(I)*10+PREX(I-1)

460 DATA SUNDAY, HONDAY, TUESDAY, MEDNESDAY, THURSDAY, FRIDAY, SATURDAY

470 DATA JANUARY, PERKURKY, NARCH, APRIL, MAY, JUNE, JULY, AUGUST, SEPTEMBER

480 DATA OCTOBER, NOVEMBER, DECEMBER

490 FOR I=0 TO 6

500 READ D$(I)

520 POR THO TO 11

530 READ M$(I)

540 NEXT I

550 REM

560 REM

CONVERT PAGE ZERO DATA INTO APPROPRIATE UNITS

570 REM

580 Y=FNR(245)+1900

590 H2=FNR(243)

600 D=FNR(241)

610 W-PEEK (239)

620 REN

630 REN

CONVERT HOURS, MINUTES, AND SECONDS INTO A

640 REM

STRING FOR "CLEANER" OUTPUT"

650 REM

660 TS-**

670 FOR I=0 TO 4

680 TS=TS+RIGHTS(STRS(PEEX(237-I)),1)

690 NEXT I

700 TS=RIGHTS(STRS(PEEX(238)-8).1)+TS

700 TS-RIGHTS(STRS(FEEK(238)-8),1)+TS

710 TS-LEPT$(T$,2)+":"+MID$(T$,3,2)+":"+RIGHT$(T$,2)

720 PRINT"TOOAY IS ":D$(W);" ":M$(M2-1);D:Y:T$

730 END

RUN

SET(S) OR READ(R) ? S

MONTH, DAY, YEAR(2 DIGITS) 7 7,18,80

DAY OF THE WEEK (1-7) 7 6

HOURS, MINUTES (24 BOUR TIME) 7 13,8

TODAY IS FRIDAY JULY 18 1980 13:08:00

SET(S) OR READ(R) 2 R

TODAY IS PRIDAY JULY 18 1980 13:09:10

```

### Machine Language Routines

Listing 1 presents machine language routines to set the clock/calendar and read the time. As shown by figure 1. PAO-PA3 go to address lines A0-A3, PA4-PA5 go to the READ and WRITE. PB0-PB3 go to data lines D0-D3, and CA2 is inverted and goes to the HOLD input.

Data to be written to the clock, and the data received from a read are stored in Page Zero locations \$E9-\$F5. These are "safe" Page Zero locations which are not used either by BASIC nor by the SYM monitor. For computers other than the SYM, other locations may have to be used, but virtually all 6502 computers will have Page Zero locations available.

The routines themselves are general routines which may be used for any 6502 computer since they do not use any monitor routines, except the routine necessary to remove the writeprotect from system RAM. Of course. the locations for the 6522 will probably be different. The machine language is located so as to occupy the highest part of memory in a 4K system. They can be easily relocated, with the only changes required being the ISR's at locations \$0FBA and \$0FDD in listing 1.

OFRC-

OFSF-

OP91-

0F94-

0F96-

0299-

OF9C-

OF9E-

OFAL-

OFA3-

OFA6-60

### Applications

The obvious use for the clock/calendar interface is setting the time and getting the time output upon request. Using the machine language routines in listing 1 in conjunction with a BASIC driver is perhaps the most convenient method of accomplishing this. Listing 2 is an example of one such BASIC program. along with two typical resultant runs. The program, in order to set the clock/calendar, merely requests the necessary data and stores it into the proper Page Zero locations and then calls the machine language routine to do the actual setting. To insure that the input data was correct, a read is done after the setting as a check. For the read operation, the program calls the machine language to do the actual reading, and then merely arranges the data obtained from \$E9-\$F5 to be output in a convenient manner.

The memory size of 4006 is for a 4K system. The dummy tape save, SAVE D. is needed to overcome a bug in SYM BASIC. The program is loaded in as file "C". The machine language routines were saved as file \$4D, so that they can be loaded by the LOAD M command.

### As mentioned previously, the clock can generate interrupts to the microprocessor. Since we are using a 6522 VIA in the interface, either of the two on-board timers can be used to generate precise interrupts of up to 0.65 seconds apart. With the MSM5832, we then can generate interrupts at one second, one minute, or one hour apart

(see figure 1 and table 2). Listing 3 presents a machine language routine to use any one of these three interrupts. Although the D1. D2 or D3 outputs could be tied directly to the IRO line of the 6502 system, in this example one of the outputs goes to the CB2 input of the 6522. The routine has been set up so that the interrupt occurs on the negative-going edge of the 122.1 microsecond pulse. If setting on the positive edge is desired, merely write a \$20 in the PCR register of the 6522. In whatever interrupt routine used with this setup, the IFR register bit can be cleared, either by directly writing into the IFR, or by reading or writing to Port B. This may be accomplished by reading the time with the routines in listing 1. Note, however, that reading the time reconfigures Port A, and this must be reset to the configuration in listing 3.

An obvious use of this type of operation would be to use an interrupt of one second when using a video display or terminal with an addressable cursor, to continually write the time in the upper right hand corner of the screen. A much more effective use would be in a polled environment where it would be desirable to get data from input ports or status of peripherals every second, minute, or hour.

Special note: The MSM5832 is a fairly new chip, first introduced in the first quarter of 1980. For this reason, it is not commonly available, except in quantity from the manufacturer. If there is sufficient reader interest in using the circuit described in this article, I can supply the chip and the 32.768 KHz crystal for \$17 plus postage. Delivery may take 4 to 6 weeks

# Listing 3: Interrupt Set-up Routines

Machine language routines for Setting up interrupts from the MSM5832 Randy Sebra July, 1980 \$8886 Un-write protect system RAM ACCESS ED Input/output register A 10842 ORA EO Data direction register 8 DORR ED SA802 DDRA EQ SA803 Data direction register A SABOD Interrupt flag register IFR EO \$A80E Interrupt enable register TER ED SOF8C Start of routine Remove write protect RAM Set up BO-B3 (data 20 86 8B SETUP JSR ACCESS #00 A9 00 LDA lines) as inputs 8D 02 A8 STA DORB Set up A0-A4 (address A9 1F LDA 412 lines and READ) as 8D 03 A8 STA DDRA 8D 01 A8 outputs and set all high 094 A9 .08 LDA \$08 Set up IPR for interrupt from CB2 8D OD A8 STA IFR Enable interrupt for A9 98 LDA 8D OE AS STA IER CD2 Return

RTS